1. INTRODUCCIÓN

Los dispositivos basados en Nitruro de Galio (GaN) son cada vez más atractivos en la electrónica de potencia ya que en combinación con el Nitruro de Aluminio y Galio (AlGaN) pueden formar heteroestructuras con un canal bidimensional de gas de electrones (2 DEG) evitando procesos de dopaje y aumentando la movilidad en el canal (Morkoç et al., 1994). Sin embargo, hay requisitos necesarios que debe cumplir una nueva tecnología de semiconductores para su amplia adopción en los sistemas de conversión de energía.

El primero es la eficiencia, y GaN ha demostrado una completa superioridad sobre el silicio (Si) debido a sus notables características electrónicas, lo que resulta en dispositivos de rápida conmutación que permiten el diseño de convertidores de alta eficiencia con baja pérdida de potencia (Alatawi, et al., 2018), (Hughes et al., 2011), (Wu et al., 2008).

El segundo es la rentabilidad. Si bien la comparación directa de costos entre las tecnologías de semiconductores es complicada debido a todos los elementos que influyen en el costo final (crecimiento epitaxial, fabricación de obleas y ensamblaje), podemos mencionar que uno de los inconvenientes de los dispositivos basados en esta tecnología es el costoso crecimiento homoepitaxial sobre sustratos de GaN. Por lo tanto, se han utilizado obleas más asequibles basadas en sustratos de silicio (GaN-on-Si) para hacerlo más competitivo en los rangos de bajo voltaje (~ 600V), pero esto hace que el dispositivo sea más vulnerable a la creación de defectos debido a la diferencia en los coeficientes de expansión térmica y al desajuste en la red (lattice) de ambos materiales (Marcon et al., 2015; Cheng et al., 2016).

El último requisito es la confiabilidad a largo plazo, es decir, la probabilidad de que el dispositivo opere correctamente en condiciones normales de funcionamiento para la vida útil prevista (Hartzell et al., 2011). La complejidad de los estudios de confiabilidad radica en que el rendimiento del dispositivo es altamente dependiente de los pasos de fabricación, el crecimiento epitaxial, las técnicas de caracterización y la variabilidad entre dispositivo y dispositivo, lo que dificulta tener una comprensión completa de los fenómenos de degradación y un consenso sobre la física detrás de los mecanismos de falla. De forma particular, los diodos de potencia basados en GaN requieren altos voltajes de ruptura (VBD) en combinación con valores bajos de voltaje de encendido (VTON), resistencia de encendido específica (RON,sp) y corrientes de fuga para reducir las pérdidas de energía y problemas potenciales de confiabilidad.

En los últimos años, se han intentado varios enfoques de procesamiento para mejorar el rendimiento del rectificador/diodo GaN-on-Si. Por ejemplo, se han adoptado estructuras usando placas de campo (field plates) simples y múltiples para aumentar el voltaje de ruptura en los diodos de barrera Schottky (SBD) y para evitar una ruptura prematura (Horii et al., 2009). Para disminuir las corrientes de fuga, se ha demostrado que el máximo campo eléctrico ubicado en la esquina del contacto de Schottky (zona del ánodo) se reduce al introducir una capa de Si3N4 para crear una terminación de borde cerrado (gated edge termination-GET) (Lenci et al., 2013).

Estudios recientes bajo estrés en estado de apagado en esta estructura han demostrado una falla relacionada a la concentración del campo eléctrico en áreas críticas como la esquina del dieléctrico que forma el GET y el borde del contacto Schottky. Se han obtenido mejoras de confiabilidad debido a una mejor distribución del campo eléctrico utilizando una capa de pasivación más delgada, una segunda capa GET, un mejor proceso de limpieza previo a la deposición en la región del contacto Schottky y una capa de cobertura de Si3N4 (Acurio et al., 2018; Acurio et al., 2019).

Si bien, los diodos de barrera Schottky con terminación de borde cerrado (GET-SBDs) han demostrado una buena confiabilidad del dispositivo bajo estrés en estado de encendido utilizando diferentes condiciones y considerando una variedad de geometrías (Tallarico, Stoffels, et al., 2016), (Tallarico, Magnone, et al., 2016), la renovada estructura de GET-SBD, que permitió la mejora mencionada anteriormente en condiciones de estado de apagado (Acurio et al., 2018), aún no se ha verificado bajo estrés en estado de encendido. Por lo tanto, la relevancia de este trabajo radica en predecir correctamente la vida útil de GET-SBDs fabricados en una plataforma tecnológica GaN-on-Si de 200V y 650V. También, en este estudio se busca demostrar que los GET-SBDs exhiben variaciones lo suficientemente bajas para realizar un análisis estadístico y extraer un componente intrínseco que no varía mucho con la ubicación sobre la oblea, lo que permitirá futuros estudios de confiabilidad intrínseca.

El resto del artículo está organizado de la siguiente manera: en la sección 2, proporcionamos los detalles de los dispositivos bajo prueba (DUT); en la sección 3 se explica la metodología de caracterización; en la Sección 4, presentamos y discutimos los resultados del análisis experimental; finalmente, en la Sección 5 se resumen los principales logros de este trabajo.

2. FABRICACIÓN DE LOS DISPOSITIVOS

La estructura simplificada de los diodos AlGaN/GaN estudiados en este artículo se muestra en la Figura 1 (a). La estructura epitaxial de la oblea de 200 mm de diámetro se hace crecer sobre un sustrato de Silicio por medio de deposición de vapor químico orgánico metálico (MOCVD). Cuenta con un sustrato diseñado para dos diferentes tecnologías, 200V y 650V. Los dispositivos tienen un canal de GaN de 300 nm de espesor, un espaciador de AlN de 0,5 nm de espesor, una barrera de Al0.25Ga0.75N de 10 nm de espesor, y una fina capa de Si3N4 de 5 nm de espesor. A continuación, el sustrato se pasiva con una capa de SiO2 y en la región del ánodo, esta capa de pasivación es removida para dar paso al proceso de grabado (etching) que reduce la barrera aproximadamente 6 nm. La estructura GET en las obleas referenciales de ambas tecnologías se obtiene depositando una capa de Si3N4 de 45 nm de espesor mediante deposición de capa atómica potenciada por plasma (PEALD) con una posterior apertura por grabado en la región central con una longitud Lsc = 5 µm, lo que da como resultado una longitud de terminación de Lg1 = 1 µm y una distancia ánodo-cátodo de Lac = 6 µm en la tecnología de 200 V y de Lg1 = 2 µm y Lac = 16 µm en la tecnología de 650 V (ver Figura 1 (b)). A continuación, se deposita y se graba metal a base de TiN sin Au para formar el contacto Schottky en la región del ánodo. Finalmente, los contactos óhmicos se fabrican utilizando una estructura de metal a base de Ti/Al. En el caso de la tecnología de 650 V, se tiene dos obleas adicionales con modificaciones en la zona GET. La primera variación es la deposición y grabación de una capa adicional de Si3N4 antes de la capa GET principal (ver Figura 1 (c)). En la segunda variación, se deposita una capa interfacial (IL) de 2,5 nm de espesor de Al2O3 seguida de una capa de SiO2 de 35 nm de espesor (ver Figura 1 (d)).

Figura 1 Esquemas simplificados de (a) los GET-SBDs utilizados para el análisis de estrés en estado de encendido. Estructura en la zona GET en (b) diodos referenciales, (c) diodos con una doble capa (Si3N4) y (d) diodos con una bicapa Al2O3/SiO2. (e) Distribución de matrices en la oblea mostrando en color azul la ubicación de los diodos medidos del lado derecho y en rojo los del lado izquierdo. (f) Diodos ubicados muy cerca dentro de una misma matriz para las mediciones de pares coincidentes

3. METODOLOGÍA DE CARACTERIZACIÓN

Las curvas IV de varios diodos en diferentes ubicaciones de las obleas demostraron un excelente desempeño en la caracterización de corriente continua (CC) a 150 ° C que es la temperatura usada para acelerar la degradación y considerar el peor de los escenarios para los dispositivos. La Tabla 1 resume los valores medios del voltaje de encendido VTON (voltaje ánodo-cátodo Vac extraído a 1 mA/mm), el voltaje directo VF (Vac a 100 mA/mm) y la resistencia de encendido RON que es la máxima pendiente de la curva IV.

Tabla 1 Valores medios de los parámetros de caracterización CC

| Tecnología | Oblea | VTON | VF | RON |

|---|---|---|---|---|

| 200V | Referencial (Si3N4) | 0,53 V | 1,32 V | 3,84 ohm.mm |

| Referencial (Si3N4) | 0,60 V | 1,83 V | 9,02 ohm.mm | |

| 600V | Doble GET (Si3N4+Si3N4) | 0,56 V | 1,98 V | 10,41 ohm.mm |

| Bicapa GET (Al2O3 /SiO2) | 0,61 V | 1,74 V | 8,67 ohm.mm |

El estrés durante el estado de encendido se realizó con el analizador de parámetros Keithley 4200-SCS manteniendo el sustrato y el ánodo conectados a tierra mientras se aplicaba un voltaje negativo entre -4V y -7V en los cátodos durante 1000 s., con lo cual se obtiene un voltaje ánodo-cátodo de estrés positivo. Con el fin de monitorear la evolución de la degradación inducida por el estrés, las mediciones se interrumpieron a intervalos de tiempo fijos utilizando la técnica de medir-estresar-medir (MSM). Después de cada interrupción, se adquirió una curva I-V y se comparó con la curva de referencia medida al comienzo de la prueba para calcular el cambio de voltaje umbral ΔVTON. Cabe señalar que se midieron un total de 64 GET-SBD con un ancho de W = 100 µm por cada oblea. Los experimentos se realizaron en grupos de diodos ubicados en el lado derecho e izquierdo de las obleas (separados 35 mm del centro de la oblea en promedio) para verificar la diferencia de degradación. Para recuperar las curvas iniciales una vez realizada la fase de estrés en todos los dispositivos, se han probado diferentes periodos de tiempo y altas temperaturas (150 ° C, 200 ° C y 300 ° C) (no se muestran los resultados por brevedad). Sin embargo, solo se obtuvo una recuperación completa sometiendo la oblea a un tratamiento térmico a 300 ° C durante al menos 30000 s (alrededor de 8 horas) para acelerar la liberación de cargas.

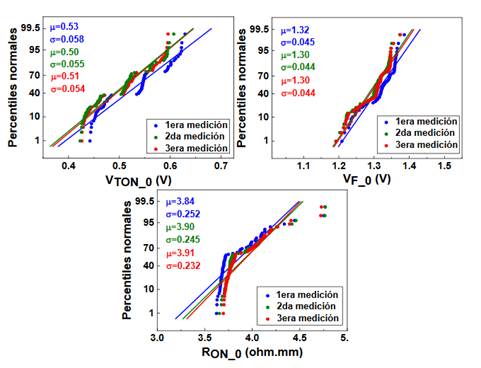

Se llevó a cabo también un análisis de repetibilidad en las obleas aplicando las mismas condiciones de estrés tres veces. Los resultados muestran que los parámetros iniciales VTON_0, VF_0 y RON_0 (parámetros extraídos de la curva IV inicial antes de que se ejecute la prueba de estrés) se vuelven repetibles justo después de la primera prueba de estrés seguida por el tratamiento térmico como se ilustra en la Figura 2 para la oblea de la tecnología de 200V. El mismo comportamiento se observa también en el resto de obleas. Por lo tanto, la primera prueba de esfuerzo actúa como una fase inicial de eliminación de trampas donde el dispositivo virgen se estabiliza liberando las cargas contenidas originalmente en los centros de captura (Acurio et al., 2017).

Figura 2 Parámetros iniciales VTON_0, VF_0 y RON_0 medidos al comienzo de tres experimentos bajo las mismas condiciones de estrés (Vestrés = 6 V, T = 150 ° C) en la oblea referencial de 200 V. Se obtiene una curva IV repetible en los GET-SBDs solo después de la primera prueba de estrés, la cual se considera una fase inicial de liberación de cargas. Adaptado de (Acurio et al., 2020)

4. RESULTADOS Y DISCUSIÓN

Al analizar la degradación después de diferentes períodos de estrés, se encuentra que una distribución de Weibull caracterizada por una función acumulativa igual a

Figura 3 Degradación ΔVF bajo Vestrés=6V a 150 °C. Se observa un comportamiento bimodal en los gráficos de Weibull, que muestra la dependencia de la degradación en la ubicación de la oblea, excepto en los dispositivos con una bicapa GET

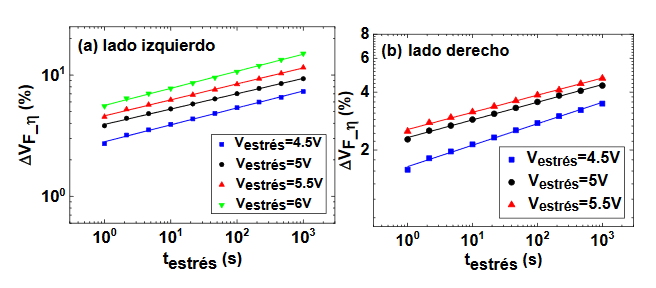

Una distribución ΔVF más estrecha se observa en los GET-SBDs ubicados en el lado derecho, lo que demuestra una mejor confiabilidad bajo condiciones de estrés en estado de encendido en comparación con los dispositivos en el lado izquierdo. Aunque el origen de la diferencia en la degradación puede ser de diversa naturaleza, podría atribuirse, por ejemplo, a cambios de espesor en las capas con centros de captura de cargas identificadas del dispositivo, como la barrera AlGaN (Tallarico, Stoffels, et al., 2016) y el dieléctrico GET. Sin embargo, todavía es necesario realizar más investigaciones para comprender mejor este fenómeno.

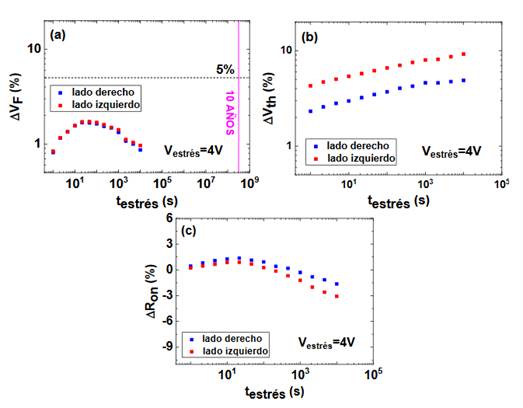

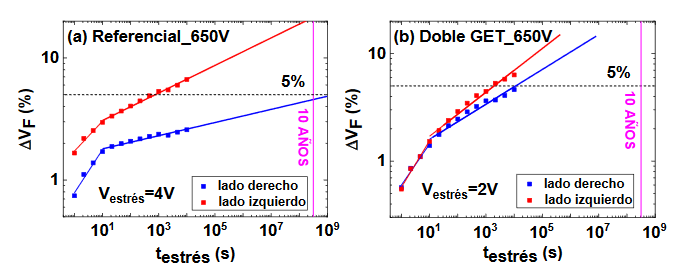

Una vez separados los datos de las dos distribuciones para cada condición de estrés, se obtiene el parámetro de escala (o valor característico) de cada distribución de Weibull para caracterizar con un único valor la degradación de la población de dispositivos correspondiente. Luego, estos resultados se grafican en función del tiempo de estrés (testrés) y se ajustan linealmente en una escala logarítmica como se muestra en la Figura 4 para determinar cuándo ∆VF alcanza el 5%, que es el criterio de falla adoptado en este trabajo. Cabe destacar que para la estimación de vida útil se ha considerado ΔVF ya que este parámetro considera tanto la degradación de VTON como de RON a través de la expresión:

Figura 4 Degradación de VF bajo diferentes voltajes de estrés usando el parámetro de escala (η) extraído de las distribuciones de Weibull de los dispositivos en el lado izquierdo (a) y derecho (b) de la oblea referencial en la tecnología de 200V. El mismo procedimiento se ha usado en las obleas referencial, doble GET y bicapa GET en la tecnología de 650V. Adaptado de (Acurio et al., 2020)

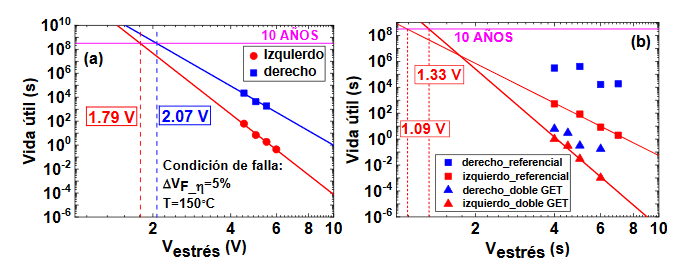

La Figura 5 (a) ilustra la vida útil extrapolada de los GET-SBDs fabricados con la tecnología de 200 V, donde 1,79 V y 2,07 V son el voltaje máximo aplicable a los dispositivos del lado derecho e izquierdo, respectivamente, para tener una degradación de VF del 5% en diez años. Para estos dispositivos, el voltaje directo nominal es de 1,32 V. Por lo tanto, la vida útil esperada es incluso superior a 10 años para todos los dispositivos de esta oblea, aunque se degraden de manera diferente. Esto demuestra que los esfuerzos para mejorar la confiabilidad en condiciones de estado apagado en esta tecnología (Acurio et al., 2018) no afectan el funcionamiento en estado encendido e incluso mejoran la vida útil esperada de estos dispositivos.

Figura 5 Extrapolación del tiempo de vida útil para los dispositivos del lado izquierdo y derecho de (a) la oblea referencial de 200V y (b) las obleas referencial y doble GET de la tecnología de 650V

Para el caso de la oblea referencial en la tecnología de 650V, no se alcanza el tiempo de vida esperado usando las tres condiciones de voltaje y la ley de potencia tanto en el lado derecho como izquierdo de la oblea como se ilustra en la Figura 5 (b). Esto se debe a que, al aumentar el voltaje de estrés, la extrapolación de la vida útil es menos dependiente de este parámetro y se empieza a observar que los valores extraídos tienden a un comportamiento más horizontal con el Vestrés, esto es más notorio en el lado derecho de la oblea referencial (cuadrados azules), por lo que no se ha incluido la curva de ajuste. Sin embargo, usando voltajes menores y tiempos más prolongados de estrés (10000 s) es posible alcanzar una vida útil de 10 años, pero solo con los dispositivos en el lado derecho de la oblea como se muestra en la Figura 6 (a).

Figura 6 Extrapolación del tiempo de vida útil usando menores voltajes de estrés y tiempo más prolongado para los dispositivos del lado izquierdo y derecho de (a) la oblea referencial y (b) la oblea con doble GET de la tecnología de 650V

Al analizar el impacto en el tiempo estimado de vida cuando se modifica la estructura del ánodo en la tecnología de 650V cambiando desde una capa simple de Si3N4 (oblea referencial) en la estructura GET a una capa adicional de Si3N4, las mediciones indican que la confiabilidad se ve comprometida al aumentar la capa adicional de Si3N4. El tiempo en el que se alcanza el criterio de falla disminuye significativamente con respecto a la oblea referencial como se observa en la Figura 5 (b). Aunque la extrapolación para los diodos del lado izquierdo muestre un mejor resultado de la vida útil esperada para la doble capa GET, se debe considerar que la oblea referencial posee una menor dependencia del voltaje de estrés que le imposibilita mejorar el resultado en la extrapolación como se ha mencionado previamente. La Figura 6 (a) y (b) permiten observar una comparación más justa de las dos obleas analizando la degradación de VF con valores de estrés más bajos y por lo tanto más próximos a los voltajes normales de operación. En esta comparación, se muestra una mayor degradación de la oblea con doble GET incluso cuando se usa voltaje de estrés menor al usado con la oblea referencial. Esto puede deberse a que el atrapamiento de cargas es más severo ya que los diodos poseen una capa adicional de dieléctrico en donde probablemente los centros de captura son mayores que con una sola capa.

En el caso de la oblea con una bicapa de Al2O3/SiO2, el tiempo de vida no ha podido ser extrapolado ya que la degradación de VF presenta un comportamiento inusual. Al comienzo del estrés, VF se degrada de manera normal. Sin embargo, a medida que aumenta el tiempo, este parámetro empieza a recuperarse indicando un punto de inversión. Esto imposibilita llegar al criterio de falla de 5% de desplazamiento en VF y extrapolar el tiempo de vida útil usando la ley de potencia. Al analizar individualmente los componentes de VF (RON y VTON) se identifica que este comportamiento se debe a una recuperación de RON durante el estrés, mientras que VTON continúa degradándose de manera habitual como se muestra en la Figura 7. El estudio de este punto de inversión está fuera del alcance de este trabajo, pero va a ser considerado para futuras investigaciones.

4.2 Extracción de la degradación intrínseca de V TON

Como se ilustra en la Figura 2, el voltaje de encendido inicial VTON_0, que se extrajo de la curva I-V inicial antes de los experimentos de estrés, no muestra una distribución de probabilidad clara. Las distribuciones más comunes, la normal (ver Figura 2) y la Weibull (no mostrada), se utilizaron para ajustar los datos. Sin embargo, la agrupación de diodos ubicados en posiciones cercanas indica una variación de procesamiento extrínseco a través de las obleas, lo que sugiere un componente extrínseco en VTON. Como resultado, VTON se puede expresar mediante la siguiente relación:

donde ΦMS es la diferencia de la función de trabajo del semiconductor de metal, 2ΦF es el potencial de superficie, QOT es la densidad de defectos de carga en el óxido/dieléctrico, COX es la capacitancia del óxido y VTON_ext es el componente extrínseco. La degradación de VTON inducida por el estrés puede ser dada por:

El componente extrínseco se debe típicamente a variaciones relacionadas con el proceso, por ejemplo, por diferencias en los espesores de las capas o variaciones de estequiometria del material a través de la oblea. Por lo tanto, la diferencia extrínseca entre dos dispositivos ubicados lejos uno del otro en la oblea es relativamente grande, pero esta diferencia debería reducirse mucho en dos dispositivos muy próximos.

Basándonos en el principio de pares coincidentes normalmente utilizados en el tiempo cero y el análisis de variabilidad dependiente del tiempo en tecnologías VLSI de escala profunda (Kaczer et al., 2015), se selecciona pares formados por dispositivos en lado izquierdo (I) y derecho (D) dispuestos muy cercanamente en la misma matriz también conocida como die (Figura 1 (f)) para obtener las diferencias de los respectivos parámetros de la siguiente manera:

donde VTON_ext, I = VTON_ext, D y consecuentemente la Ecuación (3) se puede simplificar a la siguiente expresión:

que representa la variación intrínseca de ΔVTON y donde no hay impacto del componente extrínseco. Por tanto, la degradación inducida por el estrés está directamente relacionada con el número de cargas atrapadas durante el estrés.

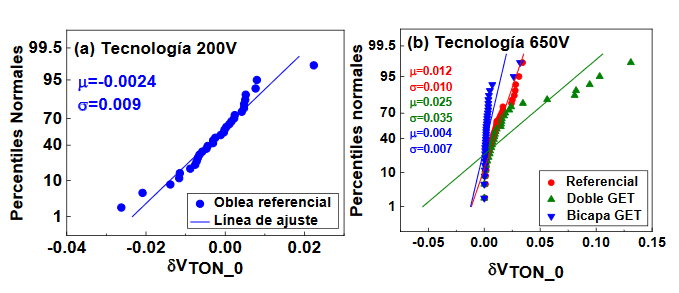

La Figura 8 muestra las distribuciones de probabilidad (normal) del cambio diferencial δVTON_0, que indica claramente una mejor uniformidad en comparación con la distribución VTON_0 de diodos individuales en todas las obleas.

Figura 8 Distribución normal del cambio diferencial δVTON_0 en (a) la tecnología de 200V y (b) 650V, respectivamente. Una vez que se elimina el componente extrínseco (sistemático), los datos pueden adaptarse mejor a las líneas de ajuste

Con esta métrica de pares coincidente la oblea con una doble GET, muestra mayor variabilidad con respecto a la oblea referencial en la tecnología de 650V como se muestra en la Figura 8 (b). Esto indica mayor variación en el proceso de fabricación, es decir, la deposición de la capa adicional no es

uniforme en todos los dispositivos.

Por otro lado, la oblea con una bicapa GET, hasta el momento ha demostrado tener mayor uniformidad en el proceso de fabricación con respecto a la oblea referencial y la hace atractiva para futuras mejoras de confiabilidad de diodos Schottky basados en AlGaN/ GaN.

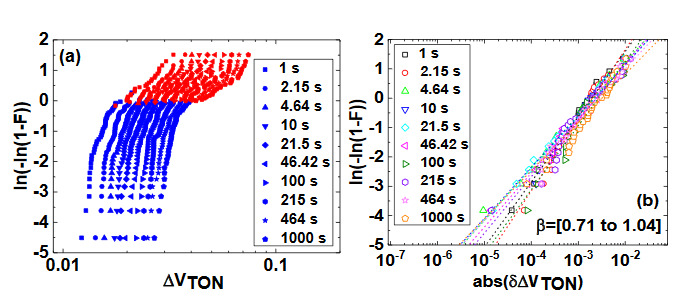

De manera similar al análisis de VTON_0, el concepto de pares coincidentes también se puede extender a las mediciones de ΔVTON siguiendo la Ecuación (5). El comportamiento bimodal que caracteriza a cada lado de la oblea desaparece convergiendo en una sola pendiente de Weibull para cada período de estrés que casi se superponen entre sí. En la Figura 9, se demuestra este comportamiento tomando como ejemplo la oblea referencial en la tecnología de 200V. Los valores bajos de β de las distribuciones δΔVTON podrían estar relacionados con una mayor variación inducida por la reducción de las muestras en la técnica de pares coincidentes. Sin embargo, la ventaja de esta técnica para extraer distribuciones de Weibull sin la influencia de cambios de espesor u otras variaciones relacionadas con el proceso se puede utilizar para futuros estudios de confiabilidad intrínseca que permitan comparaciones directas entre nuevas arquitecturas y materiales en la región GET.

Figura 9 (a) Distribución de ΔVTON para diferentes períodos de estrés (se observa dependencia en la ubicación de la oblea). (b) Distribución de Weibull del cambio diferencial δΔVTON para diferentes períodos de estrés en la oblea referencial de la tecnología de 200V cuando se aplica Vestrés=6V y T=150°C. Tomado de (Acurio et al., 2020)

5. CONCLUSIONES

En este trabajo, hemos analizado la degradación de diodos Schottky basados en AlGaN/GaN bajo condiciones de estrés en estado de encendido. Observamos un comportamiento recuperable para todos los voltajes de estrés aplicados, lo que indica que el proceso de atrapamiento de cargas ocurre mayormente en defectos preexistentes. Los dispositivos se degradan de manera diferente dependiendo de la ubicación en la oblea debido principalmente a variaciones relacionadas con el proceso. Sin embargo, se demostró mediante el uso de estadísticas más amplias que los diodos actuales de la tecnología de 200 V tienen una mejor confiabilidad en el estado de encendido con una vida útil más prolongada que en trabajos anteriores. Además, con base en la metodología de pares coincidentes, es posible reducir la componente extrínseca y/o sistemática en VTON_0 y ΔVTON para obtener distribuciones de probabilidad con pendientes de Weibull simples y bien definidas. La estructura más prometedora en la tecnología de 650 V considerando esta métrica, es aquella con una bicapa de Al2O3/SiO2 ya que muestra una menor degradación de los parámetros y exhibe mayor uniformidad en el proceso de fabricación en comparación con las otras obleas.