Introducción

La modulación por desplazamiento de fase (QPSK) es una técnica ampliamente usada en tecnologías modernas como comunicaciones satelitales, sistemas celulares, televisión digital, entre otros. Esto es debido a las características de robustez, alta eficiencia espectral y bajas tasas de error comparadas frente a otros esquemas básicos de modulación digital. D. A. B. Zambra y J. R. Pinheiro en 1 realizan un análisis del desempeño de la técnica de modulación por desplazamiento de fase, como lo es QPSK, donde describen sus ventajas. Desde su invención en la década de los años setenta, se han dedicado esfuerzos para mejorar el desempeño de dicha técnica de modulación con variaciones en los distintos componentes constitutivos tanto del modulador como del demodulador. Con la evolución de las herramientas electrónicas y computacionales se han desarrollado nuevos procesos para la ejecución de la demodulación QPSK. A continuación, se enumeran varios trabajos relacionados con este tema.

Varios autores, como K. Feher 2 han mejorado las características de la señal con técnicas de filtrado y correlación para evitar problemas de jitter e interferencia. Otros trabajos se han centrado en optimizar los recursos disponibles, Pochiraju y Fusco 3 desarrollaron un modulador con un bajo consumo de potencia para su funcionamiento en alta frecuencia. M. Raghavendra 4 diseñó un demodulador que opera a altas tasas de bits, para esto ocupa un lazo de Costas para la recuperación de los bits de datos. En 5 Lee et al. presenta un demodulador en un microcircuito con una arquitectura de submuestreo que detecta los cambios lentos de fase que resultan de un ancho de banda de recepción limitado. En 6, Takahashi et al. implementa un demodulador con circuitos integrados que incluyen una línea de retardo, amplificadores de distribución, desfasadores controlados por voltaje y detectores. Otra de las técnicas de demodulación, la presenta Wagner en 7 al utilizar un esquema de recuperación de fase basado en la detección de transiciones XOR. Finalmente, Rai y Kumar en 8 utilizan una técnica basada en windowing, transformada rápida de Fourier (FFT) e interpolación para la implementación del demodulador. En base a lo anterior se puede apreciar que son variados los enfoques para el proceso de demodulación QPSK.

Es necesario disminuir la ocupación de recursos de hardware en la recepción mediante la reducción de la complejidad de la implementación de la técnica de demodulación QPSK, por esto, es un tema de interés científico permanente, la propuesta de nuevas alternativas técnicas de demodulación. En este sentido, en este artículo se propone una nueva alternativa para recuperar los bits de la señal modulada con una cantidad reducida de recursos utilizados para la demodulación.

El presente artículo se encuentra estructurado de la siguiente forma. En la Sección II se abordan las técnicas de modulación QPSK y analizan los resultados de los moduladores diseñados en lenguaje VHDL, la señal modulada obtenida se utilizará para las pruebas del demodulador. En la Sección III se presenta la propuesta para el proceso de demodulación basada en una técnica de tendencia central. En la Sección IV se muestran y analizan los resultados de la técnica de demodulación propuesta, además se presenta la ejecución de las pruebas para evaluar su funcionamiento sobre una tarjeta FPGA Virtex-5. Finalmente, en la Sección V se describen las principales conclusiones del estudio realizado.

Técnicas de modulación QPSK

La modulación QPSK es una forma de la modulación PSK, en donde se varía la fase de la señal portadora de acuerdo a los datos de entrada.

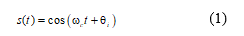

En (1) se muestra la expresión general de una señal QPSK, en donde θ i representa las fases que puede tener dicha señal y ω c es la frecuencia angular de la señal portadora:

En donde ω c representa la frecuencia angular de la portadora modulada y 𝜃 𝑖 es la fase instantánea.

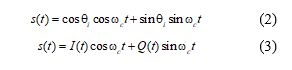

Si a (1) se aplica la identidad trigonométrica del coseno se obtiene (2), que de forma general se puede expresar como (3):

En donde 𝐼(𝑡) y 𝑄(𝑡) son las componentes en fase y cuadratura de la señal modulada respectivamente.

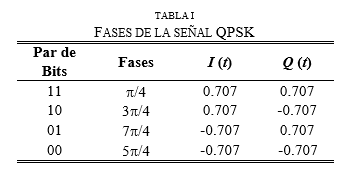

Como se puede observar en (3), la señal a la salida de un modulador QPSK convencional se forma con la adición de dos portadoras en fase y cuadratura, desfasadas 90º entre sí, es por esto que se puede ver a esta modulación como la adición de dos señales PSK binarias 9. La señal modulada QPSK tiene cuatro fases, cada una de las cuales representa a un par de bits, para obtener las fases establecidas es necesario sumar las portadoras en fase y cuadratura cada una de ellas con su respectivo valor de amplitud como se muestra en la Tabla I.

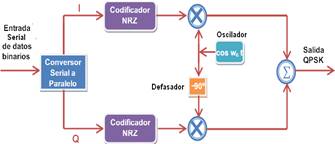

En la Fig. 1 se muestra el diagrama de bloques de dicho modulador. Los bits de datos en la entrada se convierten a una forma paralela, dando origen a los canales I (In-Phase) y Q (Quadrature), luego en ambos canales se realiza la codificación de No Retorno a Cero (NRZ del inglés Non Return to Zero) para cambiar la polaridad de los bits (0 lógico adquiere un valor de -1) y de esta manera poder efectuar la modulación de forma correcta. El bloque oscilador junto con el bloque defasador generan las portadoras en fase y cuadratura para mezclar con los bits de los canales I y Q. Por último, se tiene un bloque sumador que combina las señales obtenidas en ambos canales, obteniéndose así la señal QPSK.

Diseño del modulador con la técnica DDS

La técnica de Síntesis Digital Directa (DDS del inglés Direct Digital Synthesizer) es un método que se emplea en la generación de distintas formas de onda a partir de una referencia fija. En un sistema básico DDS se tiene un elemento de almacenamiento como una memoria, donde se encuentran las muestras digitalizadas de una señal. Estas muestras son enviadas a un conversor digital a analógico en un orden específico, de manera que a partir de la señal contenida en la memoria se puedan obtener o sintetizar otras formas de onda9.

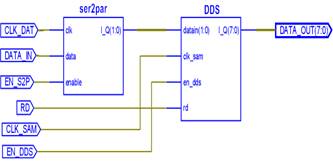

En el presente trabajo se realiza el diseño del modulador QPSK convencional con la técnica DDS para la generación de las señales portadoras y la multiplicación con los bits codificados con NRZ. Además se tiene un bloque sumador para efectuar la operación entre las señales procedentes de los canales I y Q. En la Fig. 2 se tiene el esquema de Transferencia a Nivel de Registro (RTL del inglés Register Transfer Level) de este modulador, cabe mencionar que se usó el lenguaje VHDL para su diseño y simulación. El bloque ser2par es el conversor serial a paralelo, y el bloque DDS contiene los elementos restantes.

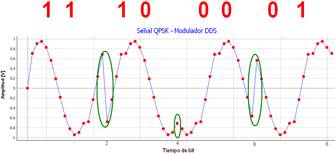

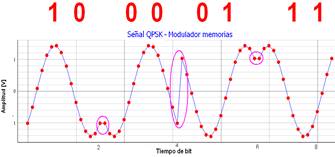

En la Fig. 3 se presenta la simulación de este diseño para una secuencia de bits: 11100001 y se resaltan los cambios de fase de la señal modulada.

Diseño del modulador con la técnica de las fases prealmacenadas

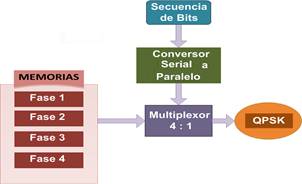

Esta metodología fue propuesta en 10. Con esta técnica en el modulador se suprimen todas las operaciones efectuadas con la técnica DDS. En la Fig. 4 se presenta su diagrama de bloques.

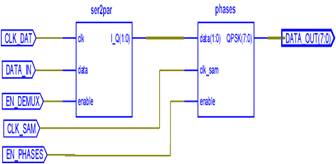

En este método se utilizan cuatro memorias de lectura, en las cuales se han guardado las señales que representan las fases de la modulación QPSK. Los datos a modular ingresan de forma serial y entran a un conversor de serial a paralelo, posteriormente los datos de forma paralela controlan un bloque multiplexor que permite elegir la fase de la señal QPSK de acuerdo a los datos que se tienen. Este diseño al igual que con la técnica DDS, se lo desarrolla en el lenguaje VHDL. La Fig. 5 muestra el esquema RTL, en donde el bloque phases contiene las memorias y el multiplexor.

En la Fig. 6 se presenta la simulación de este modulador para una secuencia: 10000111; en la gráfica se pueden observar los cambios de fase.

Demodulador QPSK convencional

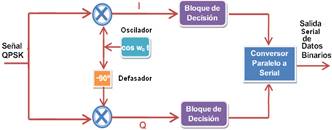

Para la demodulación de una señal QPSK se requiere recuperar las componentes I y Q, como se puede apreciar en la Fig.7. Para ello, se multiplica (mezcla) la señal QPSK con una portadora en fase y otra en cuadratura, obteniéndose las proyecciones de los símbolos QPSK sobre los ejes I y Q de la constelación.

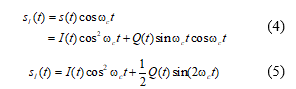

La señal QPSK recibida s (t) tiene la forma de la ecuación (3) y para la recuperación del canal I se multiplica dicha señal por la portadora en fase para obtener la señal 𝑠 𝐼 (𝑡) (véase la ecuación (4)). Si al resultado de la multiplicación se aplica identidades trigonométricas (véase ecuación (5)) se tiene recuperada la componente del canal I más componentes de alta frecuencia. Para recuperar el canal Q se realiza algo similar para obtener la señal 𝑠 𝑄 (𝑡), en el caso de la componente Q la señal recibida se multiplica por la portadora en cuadratura.

Posteriormente las componentes recuperadas son enviadas a bloques de decisión, en donde se efectúan técnicas, como filtrado, correlación u otras, que permiten recuperar los datos digitales contenidos en los canales I y Q. La técnica propuesta en este artículo consiste en aplicar un análisis estadístico a las muestras de las señales s I (t) y s Q (t) que ingresan al bloque de decisión. Posterior a dicho proceso, los datos obtenidos pasan por un conversor paralelo a serial para recuperar la secuencia de datos (bits).

Propuesta de la técnica de demodulación de la señal QPSK

La técnica que se presenta se basa en un análisis estadístico de las muestras de las señales recibidas en el demodulador y se la describe a continuación.

Al inicio, se calcula la señal s I (t) de (y 5) que resulta de la multiplicación de la señal recibida s (t) y la componente en cuadratura de la portadora (cos ω c t). Se puede comprobar que en la señal s I (t), la sumatoria de todas las muestras de la componente cos2 ω c t es mucho mayor que la sumatoria de todas las muestras de la componente sin (2ω c t), entonces se puede decir que s I (t) tiende a I (t), lo que implica que al realizar un análisis estadístico de las muestras de la señal de voltaje s I (t) es posible recuperar el valor de I (t). Mediante el análisis estadístico se determina un valor que refleja la tendencia específica de las muestras de la señal s I (t) y se procede a comparar dicho valor con un umbral para recuperar el valor de I (t) y consecuentemente reconocer el bit de datos que corresponde a la modulación de la componente en fase.

Debido a que se tiene un conjunto finito de datos (muestras) de s I (t), se puede obtener su tendencia central específica con los siguientes parámetros estadísticos 11:

Media aritmética,

Media geométrica,

Media armónica,

Mediana,

Moda,

Media truncada.

Se conoce que la media geométrica y armónica no pueden hallarse si el conjunto de datos (muestras) tienen valores menores o iguales a cero, por otro lado, la aplicación de la moda no produce resultados adecuados al compararse con un umbral. En cambio, se obtiene que la media aritmética, la media truncada y la mediana permiten determinar alguna tendencia de los valores analizados.

La mediana representa el valor de tendencia central de un conjunto de datos que han sido ordenados de menor a mayor, es decir, divide en dos partes iguales al conjunto de datos. Se tiene que la mediana es más resistente ante variaciones esporádicas externas que la media aritmética y la media truncada 11. Es por esto que la técnica de la mediana se escoge por su robustez ante datos atípicos o errados para el diseño del bloque de decisión en el demodulador. Es pertinente mencionar que la media es muy susceptible ante dichas alteraciones.

Para el cálculo de la mediana se toman en cuenta dos condiciones:

En un conjunto con una cantidad par de n muestras ordenadas crecientemente, el resultado es la muestra que ocupa la posición

En un conjunto con una cantidad impar de n muestras ordenadas crecientemente, la mediana es el promedio de las muestras que ocupan las posiciones  y

y  (muestras que están en el centro).

(muestras que están en el centro).

Resultados

Para las pruebas iniciales de la técnica de demodulación propuesta se presentan los resultados de la modulación para posteriormente demodular dicha señal.

La señal modulada QPSK tiene una frecuencia de portadora de hasta 781.25 kHz, con velocidad de transmisión de hasta 195.31 Kbps considerando una frecuencia de reloj de 50 MHz. Cada muestra tiene 8 bits y se ha establecido que la cantidad de muestras sea de por lo menos 16 por cada ciclo de la portadora.

A. Comparación de las técnicas aplicadas en el modulador

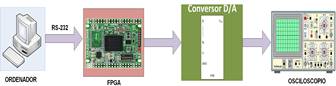

La Fig. 8 muestra el esquema de conexión usado para probar los moduladores.

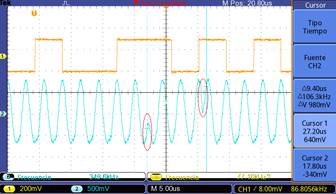

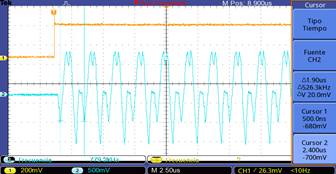

Desde el computador es posible enviar a la FPGA la secuencia a modularse a una velocidad de transmisión y frecuencia de portadora configurables. El DAC0800 conversor digital a analógico (D/A) muestra la señal QPSK modulada, y permite variar su amplitud. Con un osciloscopio se puede visualizar la señal modulada con los cambios de fase que se muestra en la Fig. 9:

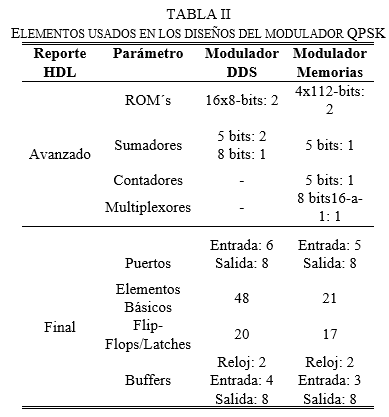

Mediante el uso de las herramientas que posee el entorno de desarrollo del fabricante XILINX 12, se obtiene el reporte de la Tabla II de los moduladores comprobados. En la Tabla mencionada se presentan los elementos usados en las dos técnicas de diseño del modulador. El modulador desarrollado con la técnica de las memorias ocupa aproximadamente el 43% de elementos básicos (tablas de consulta, compuertas lógicas, entre otros) en comparación al modulador diseñado con la técnica DDS, pero se requiere más memoria.

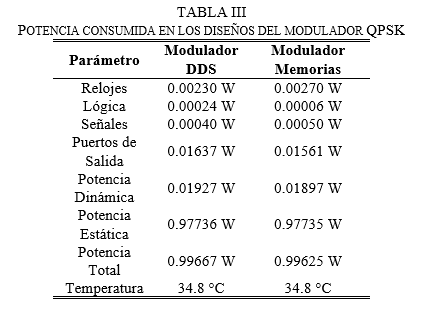

En la Tabla III se muestra la potencia consumida en los dos diseños. La potencia estática corresponde a la potencia absorbida por la tarjeta con el programa cargado, pero sin que haya estímulos externos. Y la potencia dinámica hace referencia a la sumatoria de la potencia consumida por los elementos constitutivos de los diseños y adicionalmente con la presencia de estímulos.

Se tiene que el modulador diseñado con la técnica DDS consume cuatro veces más potencia de los elementos lógicos, sin embargo en el manejo de relojes y señales su consumo disminuye en 500 μW. Con el manejo de los puertos de salida, el modulador diseñado con la metodología de memorias consume 760 μW menos. Obteniéndose que el modulador diseñado con la metodología de las memorias consume alrededor de 420 μW menos que el modulador DDS.

De esta parte se puede concluir que el modulador diseñado con la metodología de las memorias ocupa menos recursos y menos potencia.

B. Demodulador diseñado con la técnica de tendencia central

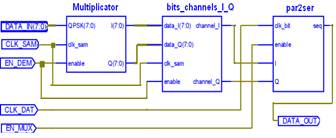

La Fig. 10 muestra el esquema RTL del demodulador QPSK, en el bloque Multiplicator se generan las señales portadoras en fase y cuadratura, las cuales se multiplican con la señal QPSK recibida. El bloque bits_channels_I_Q aloja el algoritmo de la mediana y el bloque par2ser convierte los datos demodulados que se encuentran en forma paralela a forma serial.

A continuación, en la Fig. 11, se muestra el resultado de la multiplicación entre la portadora en fase y la señal QPSK recibida, es decir se puede visualizar la señal s I (t) (señal azul). El conjunto de muestras de la última señal se analiza mediante la técnica estadística de la mediana. Algo similar se ejecuta para determinar la componente s Q (t).

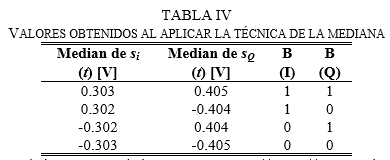

En el bloque bits_channels_I_Q que corresponde al bloque de decisión, se realiza el cálculo de la mediana. En la Tabla IV se muestran los valores obtenidos al aplicar el cálculo de la mediana de las muestras de las señales de voltaje s I (t) y s Q (t) cuando se recibe cada uno de los cuatro símbolos de una señal QPSK.

En donde Median de s I (t) y Median de s Q (t) son los valores de las medianas de las muestras de las componentes s I (t) y s Q (t), respectivamente, mientras que B (I) y B (Q) representan los bits recuperados de los canales I y Q. El umbral utilizado para realizar la decisión de los bits recuperados es el cero, y se comprueba que si el resultado de la mediana es mayor a 0, el bit recuperado es 1, de lo contrario el bit es 0.

Se comprobó que al utilizar la técnica de tendencia central propuesta es posible demodular una señal QPSK.

Evaluación del demodulador implementado en la FPGA

Para comprobar la implementación del demodulador, primero se diseñó una interfaz gráfica en el lenguaje Python13, esta interfaz permite la comunicación entre un ordenador y la tarjeta FPGA. Con la interfaz desarrollada es posible configurar la frecuencia de portadora y la velocidad de transmisión, además permite el ingreso de la secuencia a modularse.

En el proyecto para validar el funcionamiento del modulador y demodulador en su conjunto, se realizó el envío de un archivo de texto entre dos ordenadores mediante una interfaz gráfica. Se observó que la técnica de tendencia central para la demodulación de una señal QPSK funciona de acuerdo a lo esperado, los diseños propuestos y los resultados obtenidos se pueden revisar en 13.

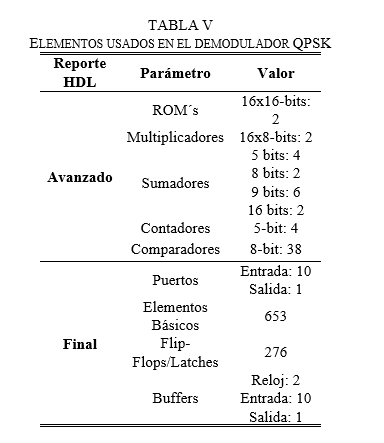

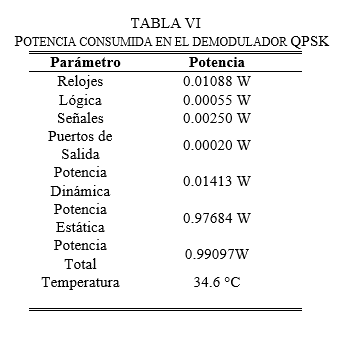

En la Tabla V se presenta el resumen de los recursos utilizados de la tarjeta FPGA para la implementación del demodulador QPSK. Para completar el reporte, en la Tabla VI se muestran los valores de la potencia consumida en la tarjeta FPGA con el demodulador.

Conclusiones

La metodología de diseño de un modulador que emplea memorias consume una cantidad reducida de recursos de la plataforma de implementación, que se refleja con una reducción de 420 de consumo de potencia con respecto al modulador con la técnica DDS. Con dicha metodología sería posible implementar otros esquemas de modulación sin alterar demasiado el software y el hardware. La técnica de demodulación basada en la mediana constituye una nueva forma de enfoque al tratamiento de las señales en el demodulador, ya que la mediana constituye un parámetro estadístico que puede ser utilizado en el bloque de decisión del demodulador para recuperar los bits de datos. El diseño e implementación del demodulador basado en esta técnica será útil en la implementación de los receptores, ya que reduce la complejidad del proceso de demodulación y conduce a disminuir los recursos utilizados del hardware de implementación. Para la implementación del demodular QPSK con la técnica de la mediana desarrollado en este estudio se requiere la ejecución de una cantidad reducida de operaciones básicas: 2 multiplicadores, 14 sumadores, 4 contadores y 38 comparadores, y el consumo de potencia llega al orden de los 991 mW. El incremento en la velocidad de transmisión y la frecuencia de la portadora implica que se requiere una mayor tasa de muestreo de la señal modulada, y por tanto, una mayor velocidad de procesamiento en la tarjeta. En futuros proyectos se propone probar las técnicas de modulación basada en memorias y demodulación basada en la mediana en ambientes con ruido. Además se realizarán estudios de la aplicación de técnicas estadísticas, como la de tendencia central, para esquemas de demodulación de orden superior.