# CONTROL DE VELOCIDAD DE UN MOTOR SÍNCRONO DE IMANES PERMANENTES ACCIONADO POR UN INVERSOR TRIFÁSICO MULTINIVEL

## SPEED CONTROL OF A PERMANENT MAGNET SYNCHRONOUS MOTOR ACTUATED BY A THREE-PHASE MULTI LEVEL INVERTER

Rosalino Mayoral Lagunes<sup>1</sup>, José Antonio Juárez Abad<sup>2</sup>, Beatriz Angélica Aguilar López<sup>1</sup>, Jesús Linares Flores<sup>2</sup>, Jorge Luis Barahona Ávalos<sup>2</sup>

### Resumen

Este trabajo presenta el diseño e implementación de un controlador robusto para el seguimiento de velocidad de un motor síncrono de imanes permanentes (MSIP). Se propone un controlador lineal basado en la retroalimentación dinámica de la salida pasiva estática del error exacto. El controlador pasivo propuesto requiere del conocimiento del par de carga, por lo que el mismo es estimado con un observador tradicional de orden reducido. El MSIP es impulsado por medio de un inversor multinivel trifásico de celdas en cascada de cinco niveles. Para la implementación del controlador, estimador y modulador multinivel se emplea un arreglo de compuertas programable en campo (FPGA) de la familia Spartan-6 XC6SLX9. El procesamiento en paralelo que provee este dispositivo permite obtener un tiempo de muestreo de 10 us. Los resultados de simulación y experimentales muestran que el controlador propuesto tiene un excelente desempeño.

**Palabras clave:** PMSM, control por pasividad, inversor multinivel, FPGA

### Abstract

This paper presents the design and FPGA embedded implementation of robust controller design to speed tracking problem for a Permanent Magnet Synchronous Motor (PMSM). Then, a linear controller based on the exact static error dynamics passive output feedback (ESEDPOF) is proposed, where the uncertainty estimation is taken into account. The technique of passivity requires knowing the load torque, this is estimated with a traditional reduced-order observer. PMSM is driven by a five levels Three-Phase Cascaded Cell Multi-Level Inverter (3Φ-CCMLI). The medium-scale field-programmable gate array (FPGA) Spartan-6 XC6SLX9 is used for implementing the ESEDPOF controller, the reduced-order observer, and the multilevel pulse width modulator. The parallel processing provided by these devices allowed to obtain a sampling time of 10us. Simulation and Experimental validation shows an excellent dynamical performance.

**Keywords:** PMSM, Passivity Based Control, Multi Level Inverter, FPGA.

<sup>1,\*</sup>División de Estudios de Posgrado, Universidad Tecnológica de la Mixteca – México.

(D) <http://orcid.org/0000-0003-3420-7416>, (D) <http://orcid.org/0000-0002-2769-4992>.

<sup>2</sup>Instituto de Electrónica y Mecatrónica, Universidad Tecnológica de la Mixteca – México,

Autor para correspondencia ✉: jbarahona@mixteco.utm.mx, (D) <http://orcid.org/0000-0001-7440-0849>,

(D) <http://orcid.org/0000-0002-5723-4786>, (D) <http://orcid.org/0000-0002-5502-6692>.

Recibido: 22-11-2019, aprobado tras revisión: 13-12-2019

Forma sugerida de citación: Mayoral Lagunes, R.; Juárez Abad, J. A.; Aguilar López, B. A.; Linares Flores, J. y Barahona Ávalos, J. L. (2020). «Control de velocidad de un motor síncrono de imanes permanentes accionado por un inversor trifásico multinivel». INGENIUS. N.º 23, (enero-junio). pp. 97-108. DOI: <https://doi.org/10.17163/ings.n23.2020.09>.

## 1. Introducción

Los motores eléctricos son actuadores que se utilizan en la mayoría de la maquinaria industrial y en electrodomésticos; su posición y/o velocidad son controladas para que puedan cumplir con alguna tarea específica, entre las que podemos encontrar: máquinas CNC, bandas transportadoras, robótica y otros procesos industriales. Dentro de estas aplicaciones es común encontrar motores síncronos de imanes permanentes (MSIP), los cuales tienen una mejor precisión en términos de velocidad y posición debido a su propiedad de sincronía. Recientemente, los controladores que permiten modificar dichas magnitudes se realizan por medio de dispositivos reprogramables y reconfigurables, tales como DSP y FPGA respectivamente [1, 2].

Para este tipo de motores se han propuesto diversos esquemas de control tales como el control basado en pasividad mostrado en [3] y el de un controlador basado en la técnica Backstepping para el seguimiento de posición el cual se muestra en [4].

Los MSIP deben ser accionados por medio de un inversor trifásico, el cual preferentemente deberá entregar una onda de voltaje con la menor cantidad de armónicos posibles, ya que en caso contrario se pueden generar algunos daños bien conocidos, tanto en la parte eléctrica como en la parte mecánica del motor [5]. En este trabajo, se construye un inversor trifásico multinivel de cinco niveles, con el cual se reduce el contenido armónico y mejorar así la calidad del voltaje de alimentación hacia el motor [6]. Una característica adicional de este tipo de convertidor es que maneja mayor potencia, pues esta se distribuye en los arreglos en serie que conforman los dispositivos de conmutación [7–9].

Este trabajo está estructurado de la siguiente manera, en la sección 2 se describe brevemente el sistema a controlar, a continuación, en la sección 3 se describe la metodología empleada centrada para la implementación de sistemas de procesamiento en FPGA tomada de [10–14]; dicha metodología posee dos fases las cuales son tratadas en las secciones 4 y 5. Posteriormente en la sección 6 se describe la construcción del convertidor de potencia empleado, en este caso el inversor trifásico multinivel de cinco niveles y finalmente en la sección 7 se presentan los resultados experimentales obtenidos.

## 2. Descripción del sistema

Se implementa un control basado en pasividad para el seguimiento suave de la velocidad de un motor síncrono de imanes permanentes, accionado por un inversor trifásico de topología en cascada de 5 niveles. Esto se realiza empleando un dispositivo de lógica reconfigurable.

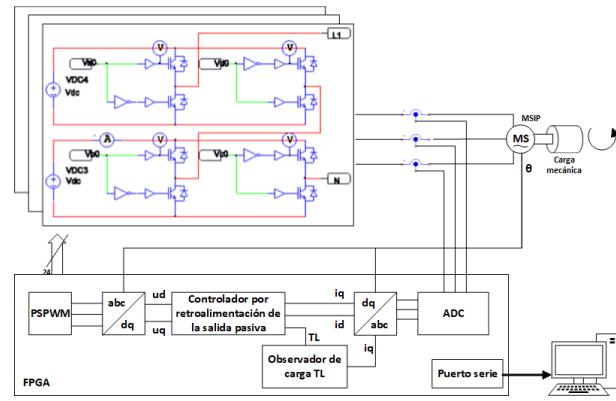

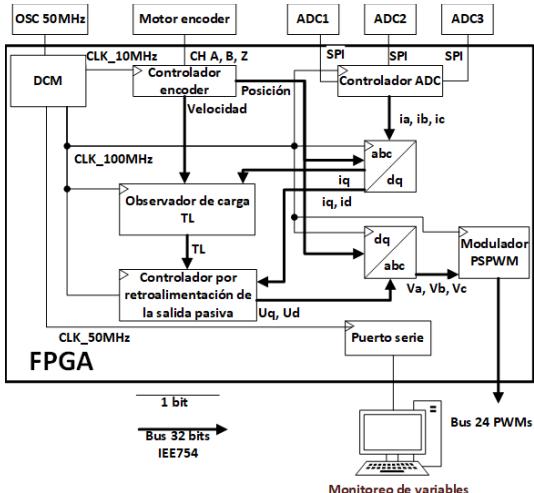

En la Figura 1 se muestra el esquema del sistema propuesto. El MSIP está accionando una carga mecánica desconocida, la alimentación del motor es suministrada por el inversor trifásico de 5 niveles. El controlador basado en pasividad, el procesamiento de señales y el modulador PS-PWM son implementados en un FPGA.

Figura 1. Esquema general del sistema.

## 3. Metodología

De acuerdo con la metodología empleada, tomada de [8], este trabajo se divide en 2 fases, la primera de las cuales, de manera general tiene que ver con el modelado del sistema y el análisis de las propiedades matemáticas de este modelo para realizar la formulación del controlador del sistema. La segunda fase trata sobre la implementación del algoritmo de control formulado en la fase 1 y los módulos complementarios los cuales serán implementados en el dispositivo de lógica reconfigurable. Cada una de estas fases se describe con mayor detalle a continuación.

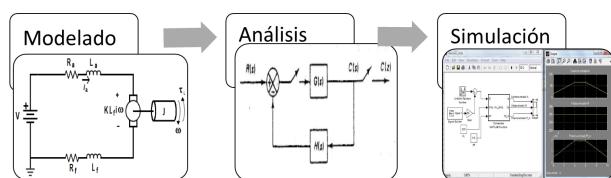

La fase 1 se resume de manera gráfica en la Figura 2. Esta fase es independiente del dispositivo a utilizar en la implementación y se divide a su vez en 3 etapas:

Figura 2. Fase 1 de la metodología.

1. **Modelado:** En esta etapa se modelan matemáticamente el MSIP y el inversor trifásico multinivel empleando las leyes o teoremas necesarios para la obtención de las ecuaciones diferenciales del sistema.

2. **Análisis:** Se analizan los modelos dinámicos de la combinación inversor-motor y por medio de

herramientas algebraicas, se diseña el controlador propuesto y se determina la factibilidad de todo el sistema.

3. **Simulación:** En esta etapa se simulan los modelos matemáticos obtenidos para confirmar la aproximación al sistema real; para ello se utiliza el *software Matlab/Simulink* en cosimulación con el *software PSIM*.

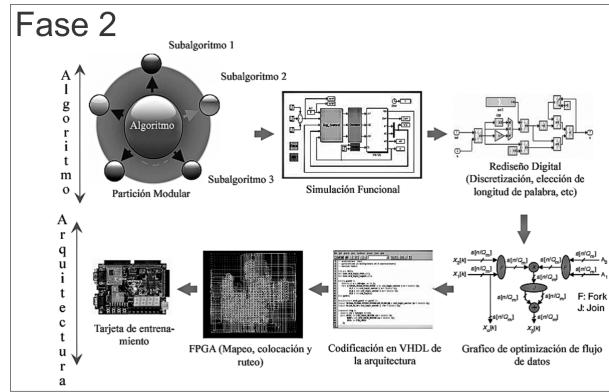

Para la fase 2, la metodología de diseño propuesta se resume en la Figura 3 la cual cuenta con 7 etapas. Esta propuesta es una solución equilibrada entre dos necesidades opuestas: 1) un método amigable que se adapta perfectamente a un ingeniero de control que no es un experto en diseño digital y 2) obtener un buen rendimiento del sistema control [10]. Las etapas mencionadas se describen a continuación:

Figura 3. Fase 2 de la metodología. [10]

1. **Partición modular:** Consiste en dividir el algoritmo en bloques reutilizables que tienen sentido desde un punto de vista funcional, es decir, el algoritmo de control y el modulador del inversor se dividen en módulos y se identifican aquellos que puedan ser reutilizables como operaciones, codificadores, tablas de búsqueda, etc. Se trata de dividir el diseño en partes más pequeñas que puedan ser manejables.

2. **Simulación funcional:** En esta etapa el controlador se valida en función de bloques en tiempo continuo empleando por ejemplo el *software MATLAB-Simulink*.

3. **Rediseño digital:** Esta etapa es muy importante, ya que se incluye la realización del filtro digital, la elección del periodo de muestreo, la elección del formato de coeficientes y variables acorde con las necesidades y restricciones del control tales como: longitud de palabra, punto fijo o punto flotante, entre otros.

Las cuatro etapas finales son para la implementación basada en FPGA y consisten en lo siguiente:

4. **Gráfico de optimización del flujo de datos:** En esta etapa se modela el flujo de datos del algoritmo para tener el mejor balance en términos de tiempo/área, para esto se obtiene una representación gráfica de cada módulo del algoritmo. La representación gráfica está compuesta de líneas y nodos, cada línea corresponde a una transferencia de datos y los nodos representan operaciones aritméticas o funciones lógicas o matemáticas.

5. **Codificación HDL:** A partir del gráfico de flujo de datos de la etapa anterior se transcribe a código VHDL; las transferencias de datos por lo regular son controladas por máquinas de estados finitos síncronas a la señal de reloj del FPGA.

6. **Implementación en FPGA:** Este es un proceso automático y es realizado por lo regular con la herramienta que proporciona el fabricante del dispositivo, en esta etapa se realiza el mapeo de las funciones resultantes, colocación y ruteo.

7. **Validación experimental:** Consiste en integrar todo el sistema, se realizan pruebas de rendimiento, y se ajustan los parámetros necesarios hasta obtener los resultados deseados.

## 4. Fase 1 de la metodología

### 4.1. Control por ETEDPOF, modelado y análisis

Partiendo del modelo  $d - q$  obtenido de las ecuaciones del modelo matemático original obtenido en [15], se calculan los voltajes de entrada  $u = [u_d \ u_q]$  y las corrientes de entrada  $i = [i_d \ i_q]$  en el eje coordenado  $d - q$ . Para el diseño del controlador se supone que se conoce la velocidad angular y el par de carga. Para comenzar con el diseño del controlador por retroalimentación de la salida pasiva, se considera el siguiente modelo en el eje coordinado  $d - q$  [3]:

$$\begin{aligned} L \frac{di_d}{dt} &= -r_e i_d + L i_q n_p \omega + u_d \\ L \frac{di_d}{dt} &= -r_e i_q + L i_d n_p \omega - K_m \omega + u_q \quad (1) \\ \frac{d\omega}{dt} &= \frac{3}{2} K_m i_q - D \omega - T_L \end{aligned}$$

Representando el sistema de ecuaciones (1) en su forma matricial y reescribiéndolo en su forma pasiva, se tiene lo siguiente [16]:

$$\begin{aligned} A\dot{x} &= [J(y) - R]x + Bu - N\eta, \quad x \in R^3, u \in R^2 \\ y_1 &= i_d \quad (2) \\ y_2 &= i_q \end{aligned}$$

Donde:

$$A = \text{diag}(L \quad L \quad \frac{2}{3}J); N = \text{diag}(1 \quad 1 \quad 1) \quad (3)$$

$$J(y) = \underbrace{\begin{pmatrix} 0 & 0 & 0 \\ 0 & 0 & -k_m \\ 0 & k_m & 0 \end{pmatrix}}_{=J_0} + y \underbrace{\begin{pmatrix} 0 & n_p L & 0 \\ -n_p L & 0 & 0 \\ 0 & 0 & 0 \end{pmatrix}}_{=yJ_1} \quad (4)$$

$$R = \begin{pmatrix} r_e & 0 & 0 \\ 0 & r_e & 0 \\ 0 & 0 & \frac{2}{3}B \end{pmatrix}; B = \begin{pmatrix} 1 & 0 \\ 0 & 1 \\ 0 & 0 \end{pmatrix}; \eta = \begin{pmatrix} 0 \\ 0 \\ \frac{2}{3}T_L \end{pmatrix} \quad (5)$$

El vector de estados está compuesto por:

$$x^T(t) = (i_d, i_q, \omega) \quad (6)$$

$J_0$  y  $J_1$  son matrices constantes y antisimétricas, y es un escalar que representa la salida del sistema y, además, es una de las variables del vector de estado  $x$ ;  $R$  es una matriz simétrica semidefinida positiva,  $B$  es una matriz constante de las entradas de control y finalmente  $\eta$  es un vector de pares de carga. Para comprobar que el sistema promedio no lineal del MSIP dado en (1) es pasivo, se hace uso de las definiciones de pasividad y dissipatividad tratadas en [3].

Sea  $u^* \in \mathbb{R}^2$  la cual denota la trayectoria de entrada nominal correspondiente a la trayectoria del vector de estado nominal  $x^*(t) \in \mathbb{R}^3$ . Partiendo de ello se construye la dinámica de referencia del sistema, la cual debe satisfacer la siguiente expresión:

$$A\dot{x}^* = [J(y^*) - R]x^* + Bu^* - N\eta^* \quad (7)$$

Se define el error de seguimiento  $e = x - x^*$ , el error de la entrada de control  $e_u = u - u^*$ , y el error de la entrada de la perturbación  $e_\eta = \eta - \eta^*$  y tomando en cuenta que  $J(y) = J_0 + yJ_1$ , entonces:

$$A\dot{e} = J(y)e - Re + Be_u + J_1x^*l_3e - Ne_\eta$$

Definiendo a  $M_3 = J_1x^*l_3$  como una matriz de  $3 \times 3$ , dada por:

$$\begin{aligned} M_3 &= \begin{pmatrix} 0 & n_p L & 0 \\ -n_p L & 0 & 0 \\ 0 & 0 & 0 \end{pmatrix} \begin{pmatrix} i_d^* \\ i_q^* \\ \omega \end{pmatrix} (0 \quad 0 \quad 1) \\ &= n_p L \begin{pmatrix} 0 & 0 & i_d^* \\ 0 & 0 & -i_q^* \\ 0 & 0 & 0 \end{pmatrix} \end{aligned}$$

Después la matriz  $M_3$  se descompone en dos matrices mediante la utilización del álgebra de matrices, y así, se consigue una matriz simétrica y una matriz antisimétrica, teniendo como resultado:

$$M_3 = \underbrace{\frac{1}{2}n_p L \begin{pmatrix} 0 & 0 & i_d^* \\ 0 & 0 & i_q^* \\ -i_d^* & i_q^* & 0 \end{pmatrix}}_{W_3} + \underbrace{\frac{1}{2}n_p L \begin{pmatrix} 0 & 0 & i_d^* \\ 0 & 0 & i_q^* \\ -i_d^* & i_q^* & 0 \end{pmatrix}}_{S_3}$$

Posteriormente  $W_3$  se suma a la matriz conservativa  $J(y)$ , y  $S_3$  se suma a la parte disipativa  $R$ . Con esta operación se consigue la ecuación de la dinámica del error de seguimiento, expresada como:

$$A\dot{e} = J^*e - R^*e + Be_u \quad (8)$$

Si se considera a  $R^* > 0$ , es decir, definida positiva entonces se satisface la siguiente condición:

$$R^* = \begin{pmatrix} r_e & 0 & -\frac{1}{2}n_p L i_q^* \\ 0 & r_e & \frac{1}{2}n_p L i_d^* \\ -\frac{1}{2}n_p L i_q^* & \frac{1}{2}n_p L i_d^* & \frac{2}{3}B \end{pmatrix} \quad (9)$$

Haciendo uso del criterio del Sylvester, se verifica que  $R^* > 0$ , es decir, que es una matriz semidefinida positiva, por tanto, se debe cumplir que:

$$\det(R^*) = \frac{2}{3}r_e B - \frac{1}{4}n_p^2 L^2 [(i_d^*)^2 + (i_q^*)^2] > 0 \quad (10)$$

Siguiendo con la metodología de diseño del controlador, mediante Lyapunov, se propone a  $e_u$  como  $e_u = -\delta B^T e$ , donde:

$$\delta = \begin{pmatrix} \delta_1 & 0 \\ 0 & \delta_2 \end{pmatrix} > 2 \quad (11) \quad \delta_1, \delta_2 > 0$$

Siendo  $\delta$  una matriz definida positiva, tal que:

$$\begin{pmatrix} u_d \\ u_q \end{pmatrix} = \begin{pmatrix} u_d^* \\ u_q^* \end{pmatrix} - \begin{pmatrix} \delta_1 & 0 \\ 0 & \delta_2 \end{pmatrix} \begin{pmatrix} 1 & 0 & 0 \\ 0 & 1 & 0 \end{pmatrix} x^* \quad (12)$$

De la Ecuación (12) obtenemos las leyes de control que actuarán sobre el sistema, quedando de la siguiente forma:

$$\begin{aligned} u_d &= \widetilde{u_d} - \delta_1(i_d - \widetilde{i_d}) \\ u_q &= \widetilde{u_q} - \delta_2(i_q - \widetilde{i_q}) \end{aligned} \quad (13)$$

#### 4.1.1. Puntos de equilibrio

Los puntos de equilibrio nos servirán para calcular las variables de referencia deseadas  $i_d^*, i_q^*, u_d^*, u_d^*, w^*$ . Para este caso  $w^*$  es el valor de la velocidad deseada que se medirá en la flecha del motor. Para obtener estas referencias se toma el conjunto de las ecuaciones (1) y se igualan las derivadas a 0, por tanto, se obtienen las siguientes expresiones:

$$0 = L\tilde{i}_q n_p \omega_d + u_d \quad (14)$$

$$0 = -r_e \tilde{i}_q - K_m \omega_d + u_q \quad (15)$$

$$0 = \frac{3}{2} K_m \tilde{i}_q - D \omega_d - T_L \quad (16)$$

Despejando se obtiene:

$$\begin{aligned} \tilde{i}_d &= 0 \\ \tilde{i}_q &= \frac{2}{3} \frac{D}{K_m} \omega_d + \frac{2}{3} \frac{T_L}{K_m} \\ \tilde{u}_d &= -L\tilde{i}_q n_p \omega_d \\ \tilde{u}_q &= r_e \tilde{i}_q + K_m \omega_d \end{aligned} \quad (17)$$

#### 4.1.2. Diseño del observador del parámetro del par de carga

Para diseñar y desarrollar un controlador eficiente y robusto, es necesario conocer todas las variables que perturban al sistema. Debido a que el controlador por retroalimentación de la salida pasiva del error, no es robusto ante perturbaciones de par de carga constante, se diseña un observador de orden reducido para estimar el parámetro de par de carga junto con los términos de fricción no modelados [17]. Se define la corriente de cuadratura  $i_q$  como la entrada de control,  $u_1 = i_q$  y se define a la velocidad angular estimada como la salida medida,  $y_1 = \omega$ . Los valores nominales de los parámetros,  $J$  y  $K_m$  se consideran conocidos. Sustituyendo las variables  $u_1$  y  $y_1$  en la ecuación mecánica dada en (1), se obtiene la siguiente expresión:

$$J \frac{dy_1}{dt} = \frac{3}{2} k_m u_1 - B y_1 - T_L \quad (18)$$

Se propone el siguiente observador de par de carga como:

$$\frac{\tilde{T}_L}{dt} = \lambda(T_L - (\tilde{T}_L)) \quad (19)$$

Donde  $\lambda > 0$ . La dinámica del error de estimación está dada por:

$$e_{T_L} = T_L - \tilde{T}_L \quad (20)$$

$$\frac{de_{T_L}}{dt} = \frac{dT_L}{dt} - \frac{d\tilde{T}_L}{dt} \quad (21)$$

Considerando  $T_L$  constante se tiene  $\frac{dT_L}{dt} = 0$ , sustituyendo (19) en (21), se obtiene la siguiente dinámica del error de estimación:

$$\frac{de_{T_L}}{dt} = -\lambda e_{T_L} \quad (22)$$

Escogiendo una ganancia  $\lambda > 0$ , el error de observación  $e_{T_L}$ , converge a cero exponencialmente cuando  $t \rightarrow \infty$ . Ahora, sustituyendo la Ecuación (18) en (19), se tiene que:

$$\frac{d\tilde{T}_L}{dt} = \lambda \left[ \frac{3}{2} K_m i_q - \left( B y_1 + J \frac{dy_1}{dt} \right) \tilde{T}_L \right] \quad (23)$$

Despejando y reordenando la ecuación anterior, se obtiene la siguiente expresión:

$$\frac{d\tilde{T}_L}{dt} + \lambda J \frac{dy_1}{dt} = \frac{3}{2} K_m u_1 - \lambda B y_1 - \lambda \tilde{T}_L \quad (24)$$

Realizando el cambio de variable  $\Psi = \tilde{T}_L + \lambda J y_1$ , se obtiene el siguiente observador de orden reducido:

$$\frac{d\Psi}{dt} = -\lambda \Psi + (J\lambda - B)\lambda y_1 + \frac{3}{2}\lambda K_m i_q \quad (25)$$

$$\tilde{T}_L = \Psi - \lambda J y_1 \quad (26)$$

El valor estimado del parámetro de par de carga junto con los términos de fricción desconocidos  $\tilde{T}_L$ , se adaptan en línea a la ley de control de seguimiento suave de velocidad angular. El propósito de esta adaptación es disminuir los efectos producidos por la carga aplicada al eje del MSIP.

#### 4.2. Simulaciones en MATLAB del controlador

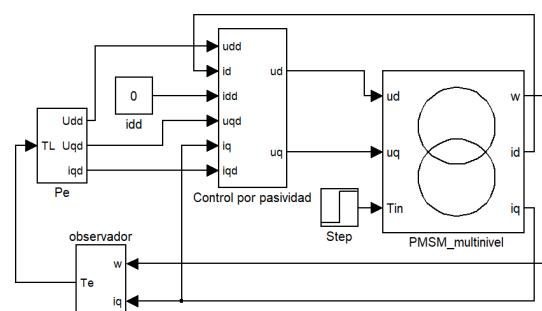

Con el uso del software MATLAB-Simulink se procede a hacer el diseño en diagrama de bloques de todo el sistema. En la Figura 4 se muestra el diagrama a bloques principal.

Figura 4. Diagrama a bloques principal.

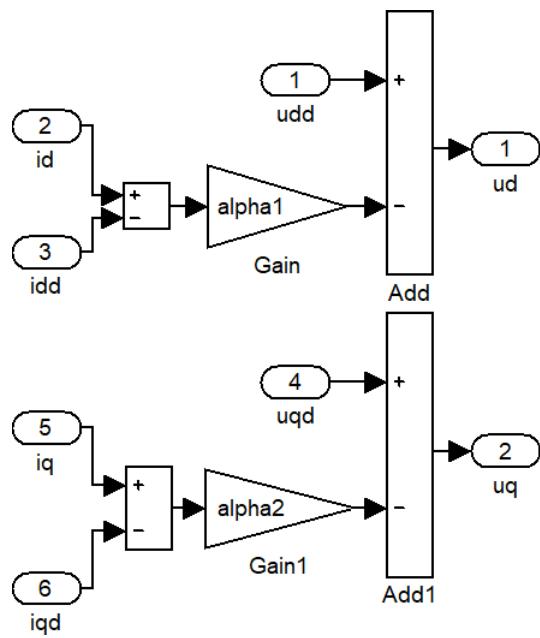

El controlador por pasividad mostrado en la Figura 4 está basado en el conjunto de ecuaciones (12), la implementación en bloques se muestra en la Figura 5.

Figura 5. Controlador basado en pasividad.

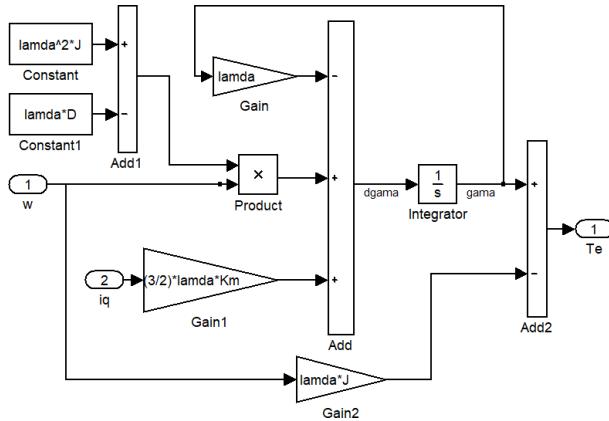

El observador de carga de las ecuaciones (25) y (26) se muestra en bloques en la Figura 6.

Figura 6. Observador de carga de orden reducido.

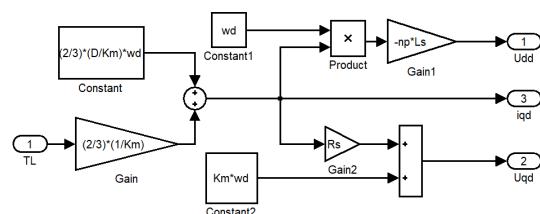

Las ecuaciones (17) de los puntos de equilibrio del sistema, que se utilizan para encontrar las referencias y trayectorias deseadas se muestran a bloques en la Figura 7.

Figura 7. Señales de referencia.

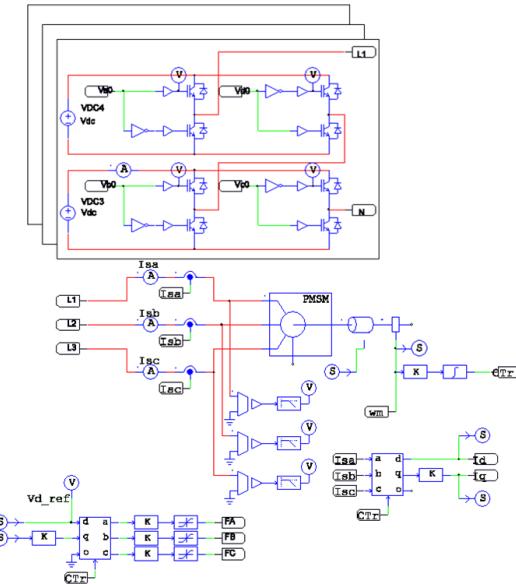

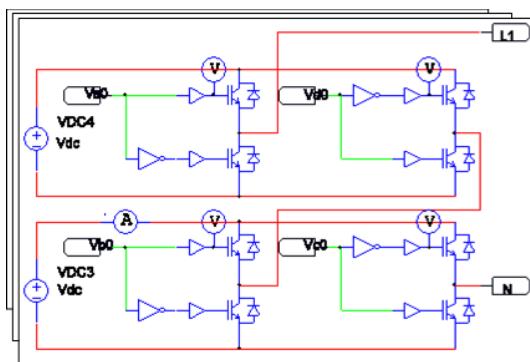

Para validar el funcionamiento del sistema se realiza la cosimulación con Simulink y Psim. El diagrama eléctrico en Psim del inversor multinivel en conjunto con el motor MSIP se muestra en la Figura 8. Se puede observar que el inversor multinivel se compone de tres secciones iguales como la mostrada en el recuadro de la izquierda de la Figura 8.

Figura 8. Diagrama eléctrico en Psim.

#### 4.3. Inversor multinivel

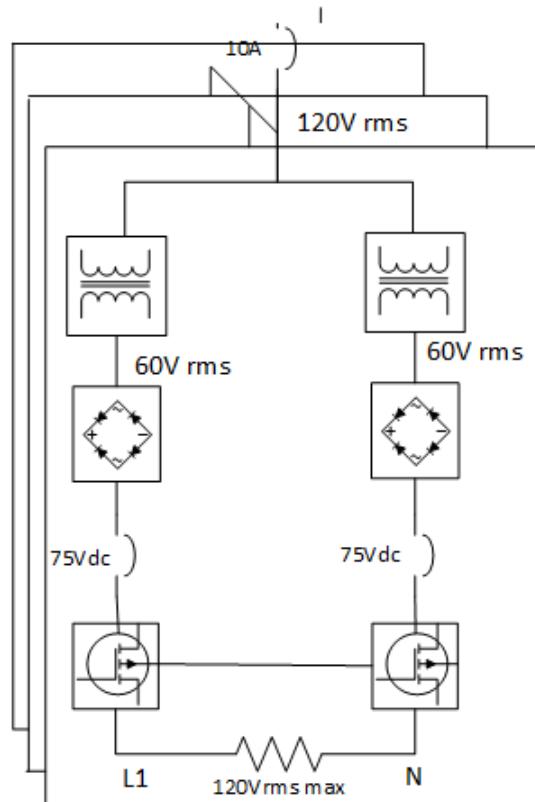

Para este trabajo se utiliza un inversor multinivel de celdas en cascada. Esta configuración se basa en celdas conectadas en serie para sumar los voltajes y obtener los 5 niveles deseados como se muestra en la Figura 9.

Figura 9. Topología del inversor en cascada de 5 niveles seleccionado.

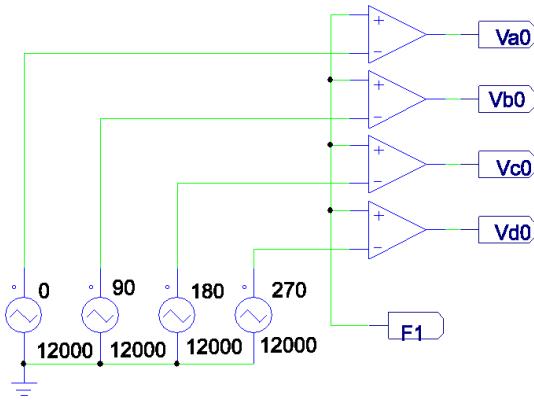

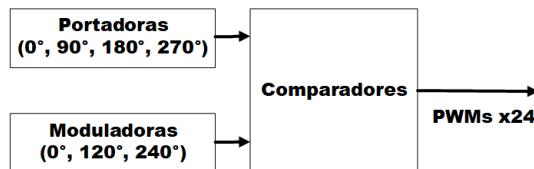

La técnica de modulación empleada es PS-PWM, la cual consiste, para el caso de un inversor de 5 niveles, de cuatro señales triangulares llamadas portadoras, desfasados entre sí  $90^\circ$ , es decir,  $0^\circ$ ,  $90^\circ$ ,  $180^\circ$  y  $270^\circ$ , respectivamente; para este caso las portadoras se generan a una frecuencia de 12 kHz. Estas señales se comparan

con una función sinusoidal llamada moduladora, para el caso en cuestión, dicha moduladora está generada por la transformación dq-abc. De manera general su funcionamiento consiste en obtener unos y ceros lógicos por medio de la comparación de la portadora y moduladora; si la señal portadora es mayor o igual a la moduladora, se obtiene un uno lógico, y en caso contrario se tiene un cero lógico. De esta manera, se generan las señales PWM que activan los dispositivos de conmutación. Cabe aclarar que cada fase contiene una moduladora desfasada  $120^\circ$  con respecto a las otras fases, por lo tanto se tiene un total de 24 señales PWM, 12 canales principales con sus 12 señales complementarias. En la Figura 10 se muestra el diagrama para generar la modulación PS-PWM solo para una fase con sus cuatro señales principales.

Figura 10. Modulador PS-PWM para una fase.

#### 4.4. Resultados de simulación

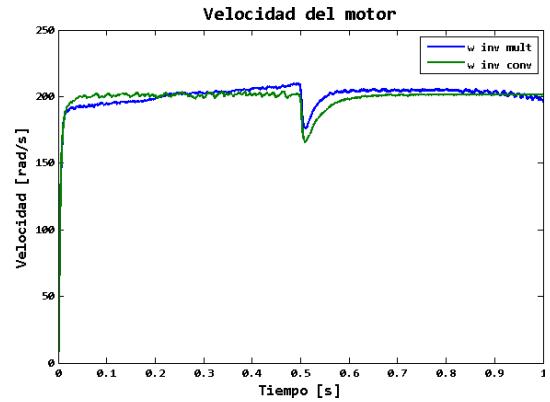

A continuación, se muestran los resultados obtenidos de la cosimulación del sistema ante diferentes escenarios y así mostrar una comparativa. Estos escenarios son: el modelo del MSIP de Psim accionado por un inversor trifásico convencional y finalmente accionado por el inversor trifásico multinivel de cinco niveles. En ambos casos es aplicado el controlador por pasividad diseñado. Como resultado de la simulación, en la gráfica de la Figura 11 se puede apreciar la velocidad angular del motor accionado ambos tipos de inversor. En dicha gráfica puede observarse que cuando se aplica un cambio en el par de carga en la flecha del motor, en el tiempo  $t = 1s$ , la perturbación provocada por dicho cambio es efectivamente contrarrestada por el controlador. No existe una diferencia apreciable entre un tipo de inversor y otro.

Figura 11. Velocidad del motor.

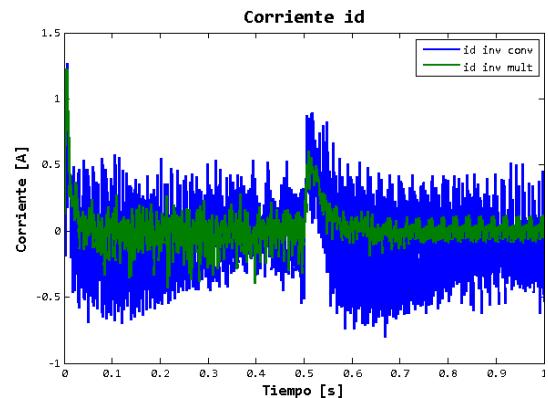

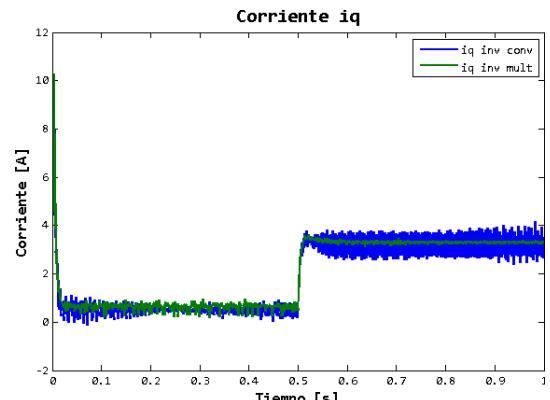

En la Figura 12 y 13 se muestran las gráficas de las corrientes  $i_d$ ,  $i_q$  respectivamente en las condiciones ya mencionadas. Es importante hacer notar que con el uso de un inversor multinivel el rizo en las corrientes disminuye de manera considerable por el uso combinado de dicho inversor y el controlador diseñado.

Figura 12. Corriente  $i_d$ .

Figura 13. Corriente  $i_q$ .

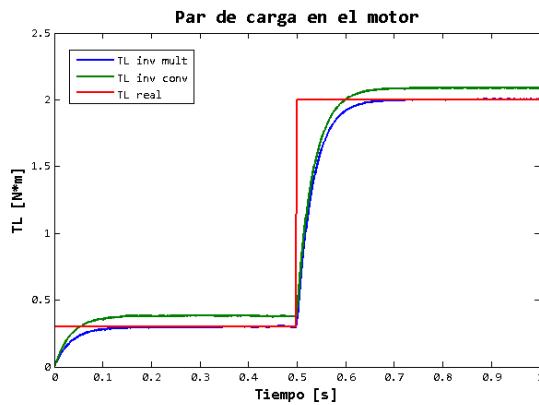

Finalmente, en la Figura 14 se muestra la estimación del par de carga. Se puede apreciar que en el observador diseñado igualmente funciona mejor en el caso del inversor multinivel, lo que comprueba su funcionamiento correcto.

Figura 14. Par de carga del motor estimado.

## 5. Fase 2

En esta fase se realiza la programación del FPGA. Cabe mencionar que en este trabajo la codificación se realiza directamente en el lenguaje VHDL, sin emplear ningún generador de código, este enfoque permite hacer uso óptimo de los recursos del dispositivo.

### 5.1. Implementación del módulo del modulador PSPWM

El modulador fue programado en el *software* ISE DESIGN de XILINX en lenguaje VHDL, por simplicidad en la Figura 15 se muestra el diseño por medio de un diagrama esquemático a bloques. Los bloques programados principales son: bloque de portadoras que es donde se generan las señales triangulares; el bloque de moduladora, es el que genera la señal moduladora; finalmente, los comparadores generan las señales PWM para realizar la comparación de las portadoras con la moduladora.

Figura 15. Diagrama a bloques del modulador.

### 5.2. Implementación del módulo del controlador

El controlador está dividido en varios submódulos: transformación abc-dq, transformación dq-abc, observador de carga, puntos de equilibrio, control de velocidad basado en pasividad, lectura de los sensores de corriente, lectura del sensor de posición/ velocidad. Estos módulos trabajan con el estándar IEEE 754 de 32 bits de precisión simple que es el formato numérico más utilizado en *hardware* [18].

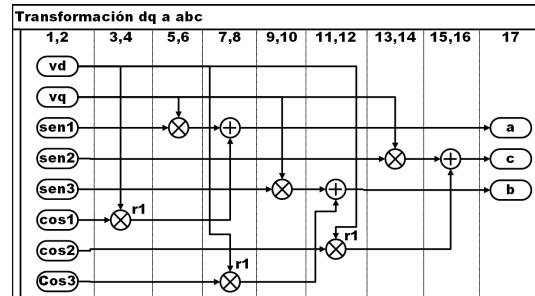

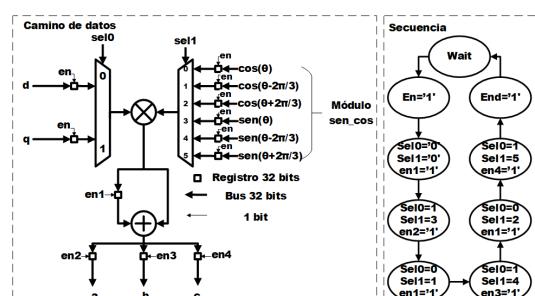

### 5.2.1. Módulo transformado dq - abc

Para el desarrollo de este módulo se realiza la arquitectura mostrada en la Figura 16, la cual es de ayuda para la solución en línea de la Ecuación (27) y la optimización de recursos. En el caso de este módulo se utiliza un multiplicador, un sumador y un registro, todos estos elementos se encuentran dentro del FPGA, sin embargo, al ser limitados se debe de optimizar su uso. Como se observa en la Figura 16, este requiere 8 entradas: d, q y las 6 funciones trigonométricas. A la salida tenemos los valores a, b y c, los cuales representan el valor del voltaje de las fases. Posteriormente en la Figura 17 se muestra la implementación en el *hardware* de las ecuaciones (27), esta metodología fue tomada de [19]. Dado la complejidad del sistema para ejemplificar el desarrollo, solo se muestra este módulo, sin embargo, la construcción de los demás módulos del sistema se realiza de manera similar. En la Tabla 1 se muestra el consumo de recursos lógicos en el FPGA después de realizar la implementación de todos los módulos implicados en el diseño y en la Figura 18 se presenta el diagrama de más alta jerarquía del sistema.

$$\begin{aligned} V_a &= V_d \cos(\theta) + V_q \sin(\theta) \\ V_b &= V_d \cos(\theta - \frac{2}{3}\pi) + V_q \sin(\theta - \frac{2}{3}\pi) \\ V_c &= V_d \cos(\theta + \frac{2}{3}\pi) + V_q \sin(\theta + \frac{2}{3}\pi) \end{aligned} \quad (27)$$

Figura 16. Diagrama de secuencia de la transformada dq a abc.

**Tabla 1.** Nivel de utilización del FPGA

| Device Utilization Summary                                      |       |           |             |

|-----------------------------------------------------------------|-------|-----------|-------------|

| Slice Logic Utilization                                         | Used  | Available | Utilization |

| Number of Slice Registers                                       | 4,038 | 11,440    | 35%         |

| Number of Slice LUTs                                            | 4,834 | 5,720     | 84%         |

| Number used as logic                                            | 4,599 | 5,720     | 80%         |

| Number used as Memory                                           | 179   | 1,440     | 12%         |

| Number of occupied Slices                                       | 1,408 | 1,430     | 98%         |

| Number of MUXCYs used                                           | 1,716 | 2,860     | 60%         |

| Number with an unused Flip Flop                                 | 1,808 | 5,107     | 35%         |

| Number with an unused LUT                                       | 273   | 5,107     | 5%          |

| Number of fully used LUT-FF pairs                               | 3,026 | 5,107     | 59%         |

| Number of unique control sets                                   | 84    |           |             |

| Number of slice register sites lost to control set restrictions | 245   | 11,440    | 2%          |

| Number of bonded IOBs                                           | 56    | 186       | 30%         |

| Number of LOCed IOBs                                            | 55    | 56        | 98%         |

| Number of RAMB16BWERs                                           | 17    | 32        | 53%         |

| Number of RAMB8BWERs                                            | 10    | 64        | 15%         |

| Number of BUFI02/BUFI02_2CLKs                                   | 1     | 32        | 3%          |

| Number of BUFI02FB/BUFI02FB_2CLKs                               | 1     | 32        | 3%          |

| Number of BUFG/BUFGMUXs                                         | 5     | 16        | 31%         |

| Number of DCM/DCM_CLKGENs                                       | 1     | 4         | 25%         |

| Number of DSP48A1s                                              | 16    | 16        | 100%        |

| Average Fanout of Non-Clock Nets                                | 3.65  |           |             |

**Figura 19.** Diagrama unifilar del inversor multinivel.

**Figura 18.** Diagrama esquemático general del sistema en el FPGA.

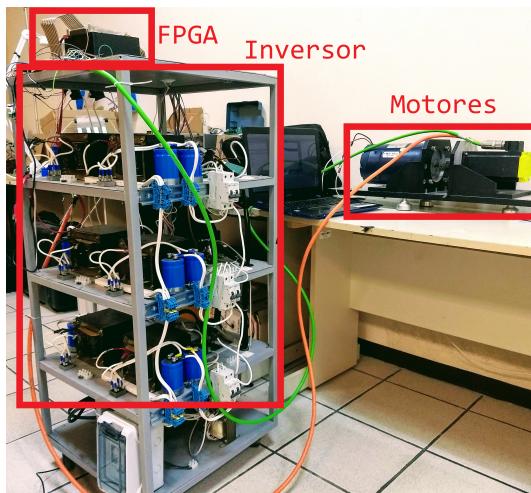

## 6. Plataforma experimental

La configuración eléctrica de la plataforma del inversor multinivel se muestra por medio del diagrama unifilar mostrado en la Figura 19.

En la Figura 20 se muestra la plataforma experimental construida y empleada para las pruebas de laboratorio. Las señales de control son generadas por el FPGA, que sirven para comutar el inversor multinivel y generar la potencia necesaria para impulsar al MSIP de acuerdo con la trayectoria de referencia deseada. La plataforma experimental está conformada por los siguientes elementos:

- Fuentes de CD aisladas

- Puentes-H

- Centro de carga principal

- Fuentes de CD aisladas

- Transformador de la fuente de CD

- Puente de diodos

- Capacitores de la fuente de CD

- Riel Din

- Clemas de conexión

- Interruptores de protección

**Figura 20.** Plataforma experimental.

### 6.1. Kit de desarrollo ALINX

El kit de desarrollo utilizado es de la marca ALINX modelo AX309 mostrado en la Figura 21, este cuenta con un FPGA SPARTAN-6 XC6SLX9, el cual es una plataforma de desarrollo de bajo costo, con las siguientes características:

**Figura 21.** Kit de desarrollo.

- FPGA model: XC6SLX9

- Tamaño 90x130 mm

- Crystal oscillator: 50 MHz

- Número de E/S de expansión: 68

- SDRAM: 256 Mbit

- FLASH: 16 Mbit

- IO port level: 3.3 V

- Serial port: onboard U transfer serial port

### 6.2. Motor síncrono de imanes permanentes

El motor utilizado es de la marca BALDOR cuyas características principales son de 1.23 kW a 4000 rpm, en la Figura 22 se muestra el motor y sus parámetros en la Tabla 2.

**Tabla 2.** Parámetros del motor

| Parámetro            | Valor        |

|----------------------|--------------|

| CAT.NO.              | BSM80N-275AF |

| SPEC.                | S2P141W042G1 |

| TORQ CONT STALL      | 3.2 NM       |

| CUR CONT STALL/A RMS | 4            |

| POWER                | 1.23KW       |

| RATED SPEED/RPM      | 4000         |

| RATED BUS VOLTS      | 300          |

| PEAK CUR/A RMS       | 14.4         |

| MAX SPEED/RPM        | 7000         |

| CLASS                | F            |

| AMB.                 | 25           |

**Figura 22.** MSIP empleado (izquierda) y motor de CD usado como carga (derecha).

## 7. Resultados experimentales

Dado que el procesamiento al interior del dispositivo FPGA es numérico, es necesario contar con un medio para obtener la lectura de las diferentes señales que se procesan, para ello se toman lecturas de las señales y se envían por medio del puerto serial/UART a una velocidad de 921 600 bps, una vez que se reciben en la computadora son procesadas y se presentan por medio de una GUI diseñada en LabView, los parámetros medidos son la velocidad ( $\omega$ ), las corrientes  $i_q$ ,  $i_d$  y el par de carga estimado (TL), cada gráfica tiene un total de 70 000 muestras en 5 segundos.

Por otra parte, el MSIP se encuentra acoplado en su flecha a un motor de corriente directa (CD) que funciona como carga mecánica externa como se puede ver en la Figura 22.

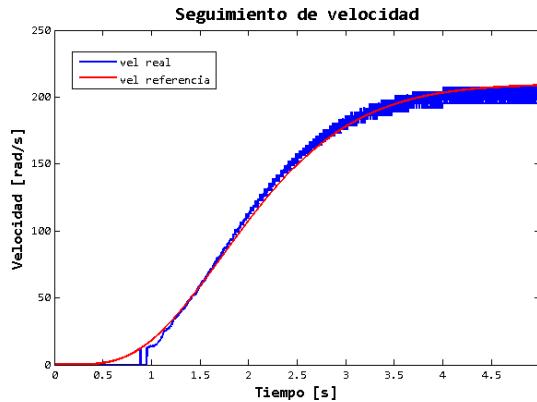

A continuación, en la Figura 23, se muestra la velocidad angular  $\omega$  medida por medio del encoder del motor. La velocidad deseada  $\omega_d$  se obtiene por medio del seguimiento de una curva obtenida partiendo de un

polinomio Bézier de 6.<sup>o</sup> orden, la cual es usada como referencia. La duración de la curva de arranque es de 5 s, después de ello se puede observar que la velocidad del motor logra establecerse en 200 rad/s como se desea. No obstante, es apreciable un rizo en la velocidad real el cual se debe principalmente al algoritmo de diferenciación numérica utilizado para obtener la velocidad a partir de las lecturas del encoder.

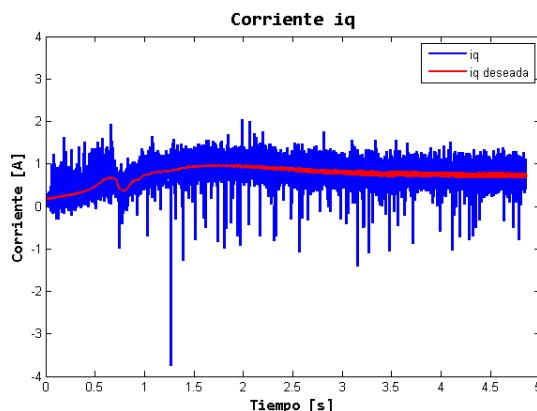

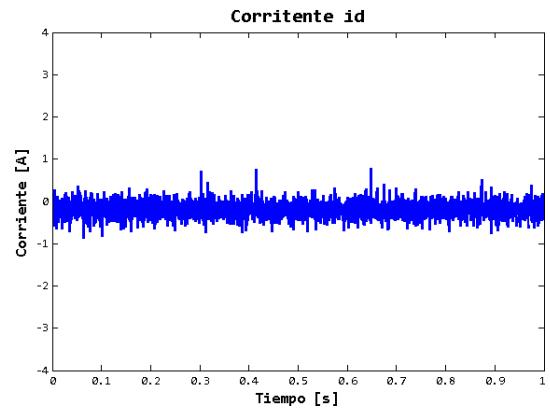

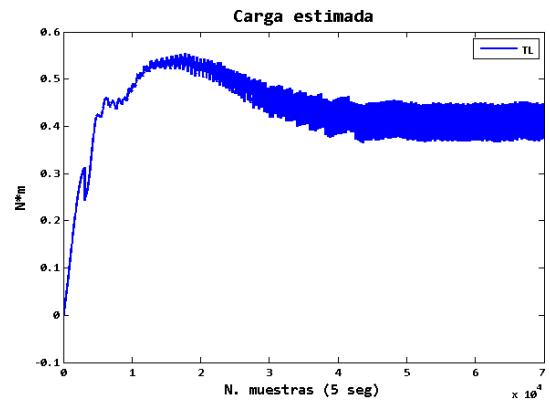

Durante el mismo periodo de tiempo en la Figura 24. se muestra el seguimiento de la corriente  $i_q$  al arranque del motor, estableciéndose en 0.5 amperes; esta es la corriente activa que es aprovechada por el motor y es transformada en par mecánico. De igual manera, en la Figura 25 se muestra la regulación de la corriente  $i_d$ , esta debe mantenerse en 0 amperes dado que es la corriente reactiva que no es posible aprovecharla. Ambas corrientes mostradas por igual muestran rizo el cual se debe a la resolución de los sensores de corriente empleados. Finalmente, en la Figura 26 se muestra la estimación del par de carga en el eje del motor durante el mismo periodo de tiempo, la cual al llegar a la velocidad deseada se establece en 0.4 Nm.

Figura 23. Seguimiento de velocidad suave al arranque.

Figura 24. Seguimiento de la corriente  $i_q$  al arranque.

Figura 25. Seguimiento de la corriente  $i_d$  al arranque.

Figura 26. Carga estimada en la flecha del motor.

## 8. Conclusiones

Con base en los resultados de simulación y los resultados experimentales se puede argumentar que el controlador por retroalimentación de la salida pasiva diseñado e implementado lleva a cabo de manera adecuada el seguimiento y regulación de la velocidad angular del MSIP. Por otro lado, se verifica que el estimador de orden reducido del par de carga, estima correctamente este parámetro. De manera adicional, en términos de hardware, se observa que el inversor multinivel reduce considerablemente la distorsión armónica de voltaje, lo que se traduce en menor ruido en el sistema en general y evita la necesidad de utilizar filtros. Gracias a las particularidades del dispositivo digital (FPGA) donde se realizó la implementación, se logra un periodo de muestreo de 10  $\mu$ s, lo que redunda en el beneficio de tener mayor velocidad de respuesta ante cambios de carga repentinos.

Como trabajo futuro se pretende implementar un algoritmo más complejo, tal como un estimador algebraico, para lograr una mejor estimación del par de carga mecánico. Lo anterior sería posible aprovechando la característica principal del FPGA que es el paralelismo.

## Referencias

- [1] T. Wildi, *Máquinas eléctricas y sistemas de potencia*, 2007. [Online]. Available: <https://bit.ly/35aPtZm>

- [2] L. Blanco Rubio, “Diseño electromagnético de un motor síncrono de imanes permanentes para el accionamiento directo de la hélice de un barco,” 2017. [Online]. Available: <https://bit.ly/2PAJZAj>

- [3] J. Linares-Flores, C. García-Rodríguez, O. D. Ramírez-Cárdenas, C. Escobar-Noriega, and M. A. Contreras-Ordaz, “Control robusto de seguimiento suave de posición angular del motor síncrono de imanes permanentes,” in *Memorias del XVI Congreso Latinoamericano de Control Automático, Octubre 14-17, 2014. Cancún, Quintana Roo, México*, 2014, pp. 1113–1118. [Online]. Available: <http://doi.org/10.13140/2.1.2760.9607>

- [4] J. Linares-Flores, C. Garcia-Rodriguez, H. Sira-Ramirez, and O. D. Ramirez-Cardenas, “Robust backstepping tracking controller for low speed pmsm positioning system: Design, analysis, and implementation,” in *2015 IEEE International Conference on Industrial Technology (ICIT)*, March 2015, pp. 2131–2138. [Online]. Available: <https://doi.org/10.1109/ICIT.2015.7125411>

- [5] IEEE, “Ieee recommended practices and requirements for harmonic control in electrical power systems,” *IEEE Std 519-1992*, pp. 1–112, April 1993. [Online]. Available: <https://doi.org/10.1109/IEEESTD.1993.114370>

- [6] M. H. Rashid, *Electrónica de potencia: circuitos, dispositivos y aplicaciones*, 2004. [Online]. Available: <https://bit.ly/2t9mZ42>

- [7] J. A. Juárez-Abad, J. Linares-Flores, E. Guzmán-Ramírez, and H. Sira-Ramírez, “Generalized proportional integral tracking controller for a single-phase multilevel cascade inverter: An fpga implementation,” *IEEE Transactions on Industrial Informatics*, vol. 10, no. 1, pp. 256–266, Feb 2014. [Online]. Available: <https://doi.org/10.1109/TII.2013.2242085>

- [8] F. Chauca Llusca, F. Llerena Rengel, and P. Chico Hidalgo, “Diseño y construcción de un inversor multinivel,” *Revista Politécnica*, vol. 33, no. 1, 2014. [Online]. Available: <https://bit.ly/36rAxpI>

- [9] L. G. Franquelo, J. Rodriguez, J. I. Leon, S. Kouro, R. Portillo, and M. A. M. Prats, “The age of multilevel converters arrives,” *IEEE Industrial Electronics Magazine*, vol. 2, no. 2, pp. 28–39, June 2008. [Online]. Available: <https://doi.org/10.1109/MIE.2008.923519>

- [10] E. Monmasson, L. Idkhajine, and M. W. Naouar, “Fpga-based controllers,” *IEEE Industrial Electronics Magazine*, vol. 5, no. 1, pp. 14–26, March 2011. [Online]. Available: <https://doi.org/10.1109/MIE.2011.940250>

- [11] D. G. Maxinez and J. Alcalá Jara, *VHDL: el arte de programar sistemas digitales*, 2002. [Online]. Available: <https://bit.ly/2PCE8dL>

- [12] J. J. Rodríguez-Andina, M. D. Valdés-Peña, and M. J. Moure, “Advanced features and industrial applications of FPGAs—a review,” *IEEE Transactions on Industrial Informatics*, vol. 11, no. 4, pp. 853–864, Aug 2015. [Online]. Available: <https://doi.org/10.1109/TII.2015.2431223>

- [13] W. Zhu, “Fpga logic devices for precision control: An application to large friction actuators with payloads,” *IEEE Control Systems Magazine*, vol. 34, no. 3, pp. 54–75, June 2014. [Online]. Available: <https://doi.org/10.1109/MCS.2014.2308691>

- [14] E. Mandado, L. J. Álvarez, and M. D. Valdés, *Dispositivos Lógicos Programables*, 2002. [Online]. Available: <https://bit.ly/38uCieq>

- [15] R. Krishnan, *Permanent Magnet Synchronous and Brushless DC Motor Drives*, 2017.

- [16] H. J. Marquez, *Nonlinear control systems: analysis and design*. Wiley-Interscience Hoboken, 2003, vol. 1. [Online]. Available: <https://bit.ly/2YMdMKM>

- [17] Y. E. Gliklikh, “Necessary and sufficient conditions for global-in-time existence of solutions of ordinary, stochastic, and parabolic differential equations,” *Abstract and Applied Analysis*, vol. 2006, Special Issue, p. 17, 2006. [Online]. Available: <https://doi.org/10.1155/AAA/2006/39786>

- [18] IEEE, *IEEE 754-2019 - IEEE Standard for Floating-Point Arithmetic*, 2019. [Online]. Available: <https://bit.ly/2E5tnvo>

- [19] M. Naouar, E. Monmasson, A. A. Naas-Sani, I. Slama-Belkhodja, and N. Patin, “FPGA-based current controllers for AC machine drives—a review,” *IEEE Transactions on Industrial Electronics*, vol. 54, no. 4, pp. 1907–1925, Aug 2007. [Online]. Available: <https://doi.org/10.1109/TIE.2007.898302>